UPF was created to go beyond what HDL can do for managing on-chip power. HDLs are agnostic when it comes to dealing with supply & ground connections, power domains, level shifters, retention and other power management related elements of SoCs. UPF fills the breach allowing designers to specify in detail what parts of the design are connected to what supply and ground lines. It also allows implementation of a wide range of necessary additions to make on-chip power management work. Thus, HDL and UPF have been designed to work together to allow a complete definition of the design. Implementation and verification tools have evolved to support HDL and UPF together. Yet there has been a hole in probing UPF dynamic objects during simulation.

A white paper from Siemens EDA, formerly Mentor, describes a methodology developed for solving this problem. The paper written by Progyna Khondkar titled “Probing UPF Dynamic Objects: Methodologies to Build Your Custom Low-Power Verification” was presented at DVCon Europe 2020. The author found a problem with monitoring the state of various power state transitions. Without this it is hard to create verification environments that can work effectively.

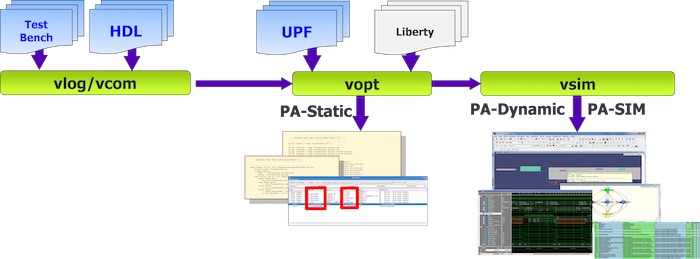

The paper provides an overview of the basic elements of a UPF implementation. This includes a definition of UPF itself, followed by descriptions of UPFIM (UPF Information Model), the processing stages and UPF’s bind checker command. There are two APIs for accessing the UPFIM: Tcl and the native SystemVerilog HDL API. Simulation related controls are enabled during phases 3 to 5 – compilation of HDL code, elaboration & optimization and execution of the simulation. Because the UPFIM database is created at the end of the optimization step, there are limitations on accessing it for custom verification productivity.

The paper presents an approach for allowing UPF processing at the design elaboration and optimization steps so that the necessary data is available through the APIs. The query functions needed for dynamic query are: upf query object properties, upf query object pathname, upf query object type, and upf object in class. Their proposed use model relies on the Tcl API query to UPFIMDB used together with bind checker whose interface uses the corresponding SV HDL native representation types.

The author provides code snippets for the SystemVerilog assertion checker. This is followed by an example of the UPF bind and query functions for their retention checker example. Then the transcript for the results are shown with the output of the assertion checks. The simulator used in the example is the Siemens EDA Questa Power-Aware simulator. The author summarizes the new methodology and shows that it is effective in providing a way to continuously probe UPF dynamic objects.

The Questa Power-Aware simulator has outstanding IEEE 1801 UPF standard support, providing processing capabilities such as: architectural analysis, the latest UPF 3.1 simulation semantics with built-in dynamic PA checkers, extensive reporting for insight into the behavior of the power management system, and advanced power-intent debug. Questa also provides users with automated PA coverage and test plan generation driven from a UPF file.

UPF has already proven itself effective for capturing and implementing complex power management regimes. Many of today’s advanced products would not be feasible to implement without it. Of course, UPF has a long history and has gone through many revisions – each of which has allowed it to become more useful and comprehensive. This paper shows an interesting way to expand the verification capabilities of UPF in simulation flows. The full paper with references can be found here for download.

Also Read:

Calibre DFM Adds Bidirectional DEF Integration

Automotive SoCs Need Reset Domain Crossing Checks

Siemens EDA is Applying Machine Learning to Back-End Wafer Processing Simulation

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.