Design for test (DFT) requires a lot of up-front planning that can be difficult to alter if testing needs or performance differ from initial expectations. Hierarchical methodologies help in many ways including making it easier to reduce on chip resources such as the number of test signals. Also, hierarchical test allows for speed-ups from parallel testing of separate blocks. MUX’ing of test signals helps deal with limited test pins on SOCs, and also reduces wiring overhead. Yet with each of these advantages comes the need to plan accordingly. Mentor has just announced what they call Streaming Scan Network (SSN) in their Tessent product line that promises to offer increased flexibility and performance. Tessent’s SSN offers support for implementation of a specialized network for carrying test data within an SOC.

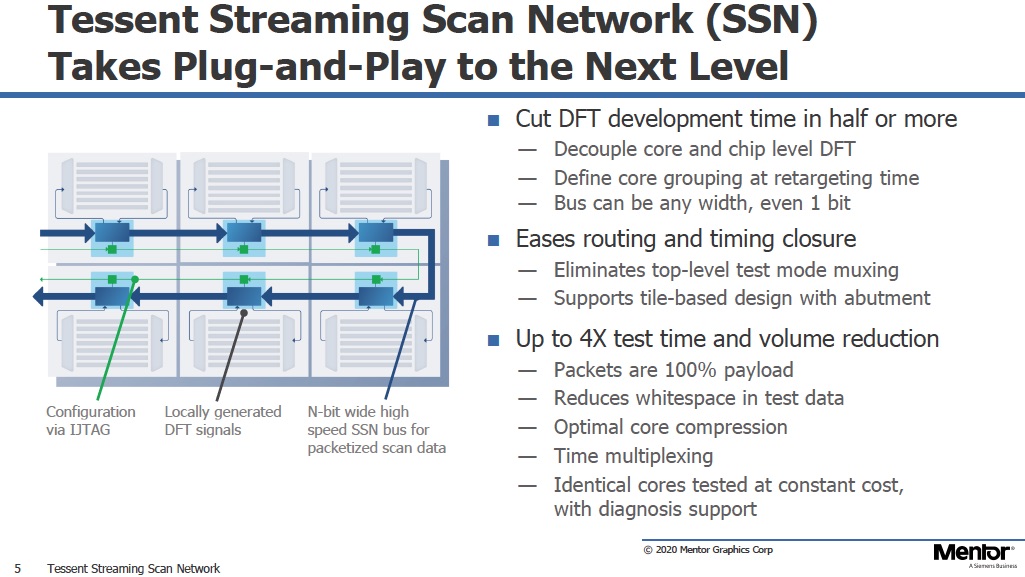

While at glance it might seem that a Network On Chip (NOC) similar to those used for block level data buses would suffice, however Mentor has developed a highly optimized solution that better meets the needs of DFT in several clever ways. The Streaming Scan Network bus width is independent of the number of the block level scan pins. For instance, a 4 bit wide SSN bus can carry 7 bits for one block and 5 for another, interleaving the bits on the SSN bus. In fact, the SSN bus could even be 1-bit wide if needed and still be used for cores with any number of test pins. There is a controller at each core node that manages the incoming and outgoing test data and transfers it to and from the block’s scan pins. The controllers have their own command line that directs their activity. Because once streaming starts there is no header information required, the SSN bus is carrying 100% payload. This is why for test SSN is a better solution than traditional NOCs.

The grouping of cores for parallel testing can be easily reconfigured because the targeting of test data is handled by the node controllers. So, if in the late stages of product development, a specific block’s test vector size increases, no hardware changes are needed. Also scan and capture can now be handled flexibly and do not have to align with other blocks being tested at the same time. If there are blocks that require larger vectors, they can get priority, so their tests can complete sooner. This makes it possible to optimize and save tester time.

So, what are the results of using the Streaming Scan Network? Mentor worked extensively with Intel prior to the announcement. In fact, Intel published a paper at the 2020 ITC that goes into the details of the improvements they observed. Intel reports that they found that SSN reduced test data volumes by 36 to 43%, reduced test cycles by 16 to 43%. They were able to run the steps in the design and retargeting flow between 10-20X faster when compared to their previous methodology.

Mentor claims that DFT development time can be cut in half or more with the application of Streaming Scan Networks. Also, because it also supports abutment-based design styles, it is useful in many of the newer tile based designs found in AI and other parallel processing applications.

Mentor has shown a consistent history of aggressive technology development in test. The recent advances in their Tessent product are impressive. Although, in hindsight it seems inevitable that a packet based methodology would be advantageous for DFT, Mentor has taken the time to develop a well thought out approach that is well suited for test in particular. More information about Mentor’s Streaming Scan Network in Tessent can be found on the Mentor website.

Also Read:

Mentor User2User Virtual Event 2020!

ASIC and FPGA Design and Verification Trends 2020

Siemens is the True Catalyst for Secure and Trusted Digital Transformation

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.