It has become a cliché to start a blog post with a cliché, for example “Chip designs are forever getting larger and more complex” or “Verification now consumes 60% of a project’s resources.” Therefore, I’ll open this post with another cliché: “Designers need to know only one language, but verification engineers must know many.” This statement has been around since the earliest days of Verilog and VHDL for RTL-based design. Neither of those hardware description languages (HDLs) offered the full set of programming capabilities needed for verification environments. At a minimum, verification engineers would also use C, often linked to the HDL code by the Programming Language Interface (PLI) or something similar. Of course, the claim that designers needed only to know RTL was a stretch. Both design and verification engineers were well versed in the Unix toolkit (shell scripts, awk, sed, etc.) and some of these utilities surely qualified as languages.

It is true that the demands on verification engineers for new languages and formats grew faster than on designers for many years. Perl, Python, and Tcl appeared frequently in verification environments. Verification engineers added object-oriented programming (OOP) with e, C++, and SystemC , and the rise of formal verification introduced a wide variety of exotic assertion and property languages. The landscape changed again with the introduction of SystemVerilog. Although most designers paid little attention to its OOP features, they had to master other aspects of a language much more complex than Verilog or VHDL. Some became proficient in SystemVerilog Assertions (SVA) since their design knowledge enabled white-box properties and more thorough formal verification. These trends have continued. Many newer standards such as SystemRDL, Unified Power Format (UPF), and Portable Stimulus Standard (PSS) require input from both design and verification engineers. Today, everyone developing chips must be comfortable working with multiple languages.

What does this all mean for EDA tools that deal with languages? To get some answers, I checked in with Cristian Amitroaie, CEO of AMIQ EDA. They provide Design and Verification Tools (DVT) Eclipse Integrated Development Environment (IDE) and Verissimo SystemVerilog Testbench Linter, both of which are all about compiling and understand complex languages to make coding more efficient and more accurate. Cristian confirmed my observation that the number of languages and file formats in use on chip projects has grown a lot in recent years, and that both design and verification engineers are affected. He said that AMIQ is seeing a leap in designer usage of their tools, perhaps driven in part by the new requirements as well as increased design size and complexity. Over the years, they have added support for many new languages in DVT Eclipse IDE. Cristian walked me through some of the tool’s capabilities, and I jotted down a few notes.

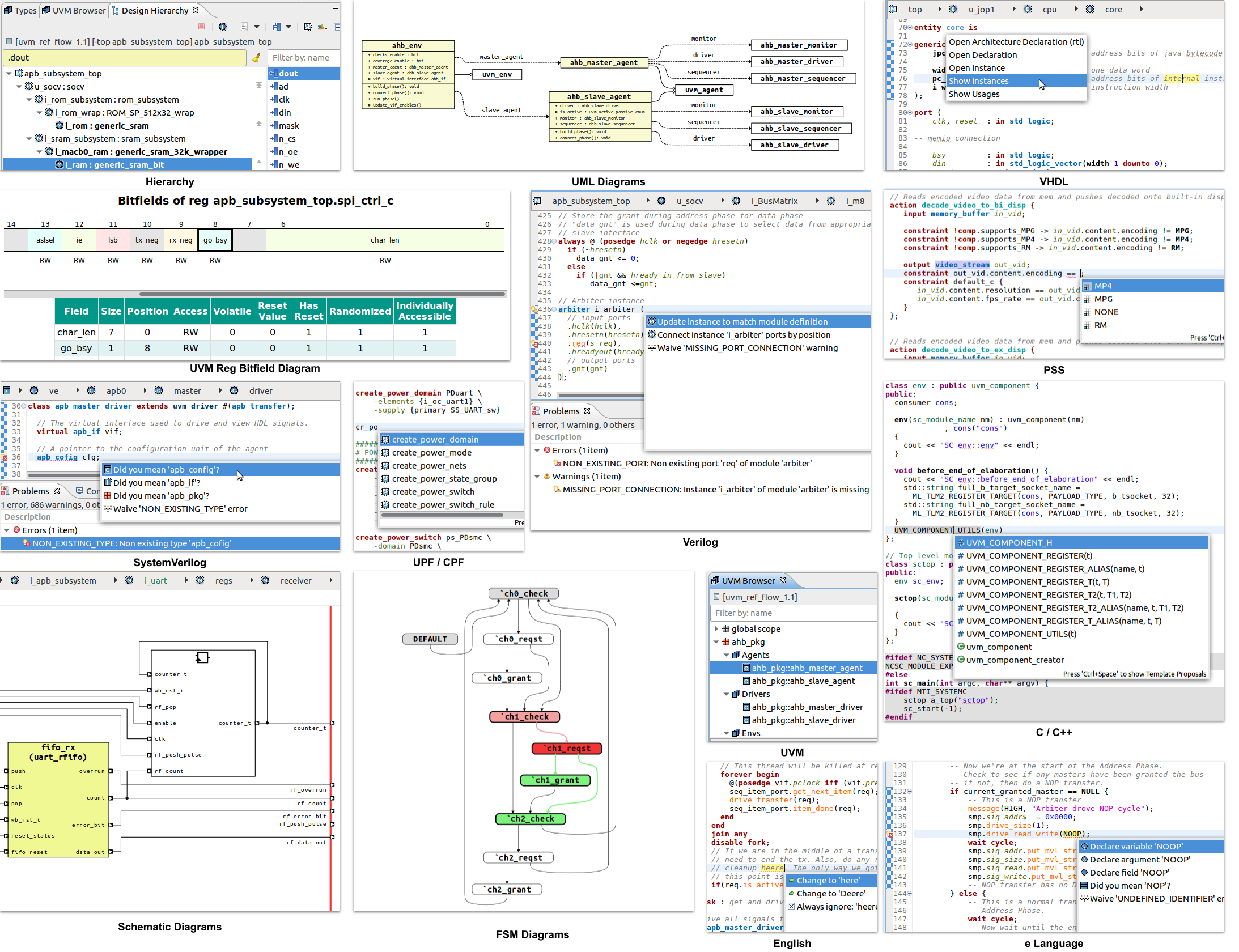

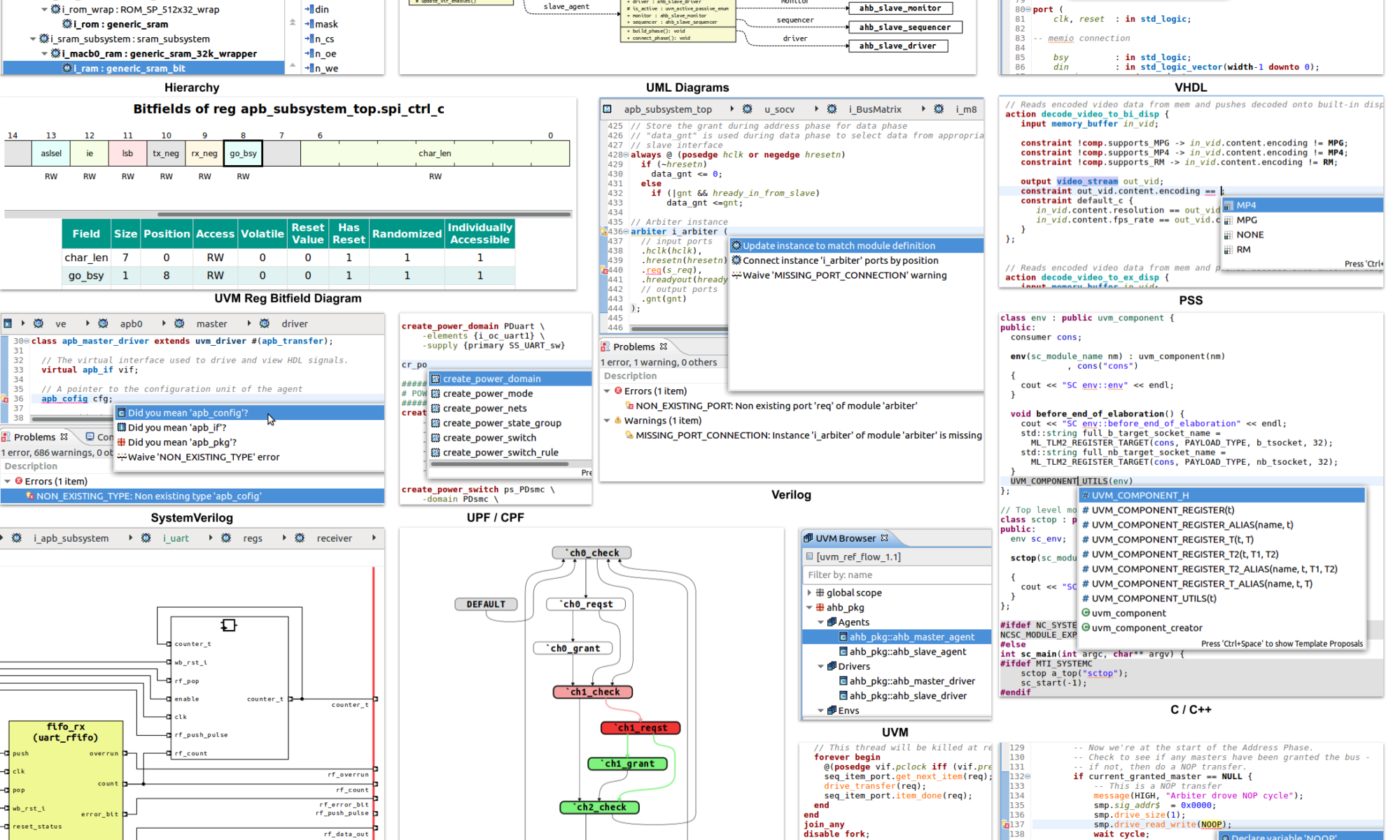

For designers, the combination of easy RTL entry and efficient tracing through the design is the most important role of an IDE. For Verilog, VHDL, and the synthesizable subset of SystemVerilog, the IDE is a much better vehicle for design capture and exploration than traditional text editors. Every time that a new file is opened or new code is entered, the IDE compiles it, checks for correctness, and updates its internal model. Errors are detected on the fly, with suggestions for fixes plus templates for new code to be added. Users can follow signals throughout the design without having to search multiple files.

The same capabilities are available to verification engineers, especially when Verissimo is added for deep and sophisticated testbench checks. The IDE understands the OOP features of SystemVerilog and e, including the key concept of extending classes. Since most testbenches today are compliant with the Universal Verification Methodology (UVM), the IDE has built-in knowledge of the UVM library. AMIQ has added support for UPF power intent files and PSS models as well. The C/C++ Development Tooling (CDT) Project provides a fully functional C and C++ Eclipse-based IDE. DVT Eclipse IDE includes this environment and provides links to connect C/C++ with the other languages supported. As a writer and editor, I couldn’t help noticing that AMIQ even provides an English spell-checker to detect typographical errors in comments and text strings. Offhand, I can’t think of anything they’ve missed.

Cristian mentioned three additional points that struck me as important. First, he noted that AMIQ provides a consistent level of capabilities for all design and verification languages. This makes it easy to move from one language to another with a familiar graphical interface and available commands. This is one aspect of a seamless experience in a multi-language environment, but his second point was that users must be able to navigate across language boundaries in a transparent way. This is possible because DVT Eclipse IDE’s unified internal model includes all aspects of the verification environment and the design, spanning all languages. Users can click hyperlinks from one language to another, jumping among source code editors, schematics, hierarchy browsers, and Unified Modeling Language (UML) diagrams.

Cristian’s final point concerned their choice of the “DVT Eclipse IDE” name. Their solution has never been just about Verilog, VHDL, RTL, or verification languages. “Design and Verification Tools” was chosen because they built an IDE for all engineers involved in chip development, no matter their specific roles or languages used. The result is a unified, efficient, and easy to use cockpit that blurs language boundaries.

I’d like to thank Cristian for his thoughts on our multi-language chip development world and for his team’s efforts to make it possible to be a true polyglot engineer. I’ll bet that there will even more languages coming along in the future, and I expect that AMIQ EDA will keep up with them.

To learn more, visit https://www.dvteclipse.com.

Also Read

An Important Step in Tackling the Debug Monster

Debugging Hardware Designs Using Software Capabilities

Automatic Documentation Generation for RTL Design and Verification

Share this post via:

Comments

One Reply to “The Polyglot World of Hardware Design and Verification”

You must register or log in to view/post comments.