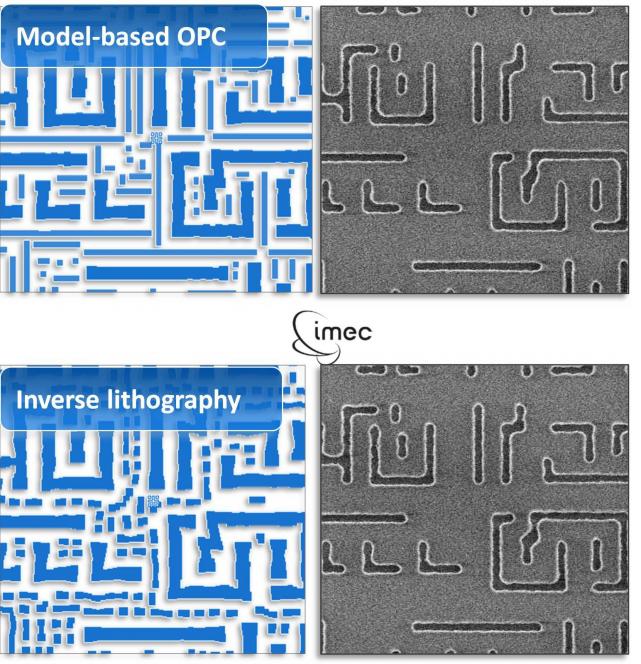

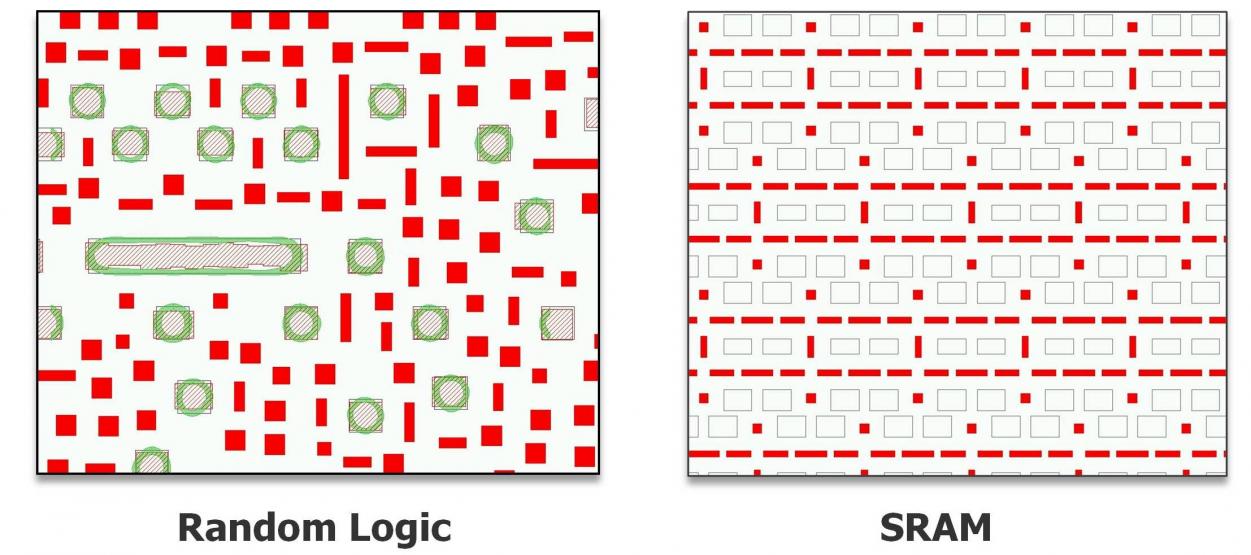

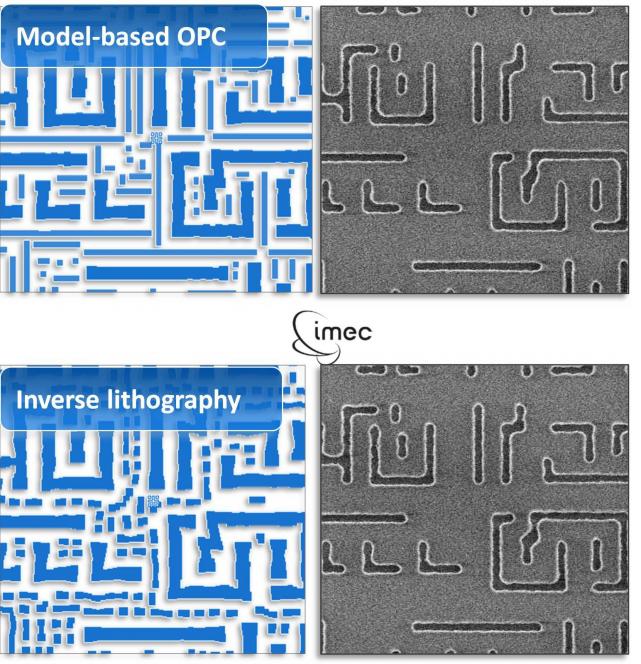

It appears that immersion lithography is now the plan of record for manufacturing ICs at 14nm. How is it possible to use 193nm wavelength light at 14nm? How can we provide the process window to pattern the such tight pitches? The secret lies in computational lithography.  For 20nm, the two key innovations in computational lithography involve enabling double patterning with concurrent OPC, and in improving difficult-to-print layouts with localized in-situ optimization and by using an inverse lithography technique.For 14nm, says Mentor Graphics’ OPC product marketing manager Gandharv Bhatara, computational lithography offers more tools for process window enhancement with better approaches to sub-resolution assist features (SRAFs). SRAFs have been used since the 130nm node for resolution enhancement, but for 14nm, SRAF placement has evolved considerably. In a recent article, Bhatara says that SRAF placement has moved from rules-based to model-based, and describes two new model-based approaches developed in the Mentor OPC tools. One approach uses inverse lithography (ILT) to create the golden reference for a rules-based SRAF placement. This gives superior process window for critical blocks like SRAM, where the rules are relatively easy to develop. The second approach is a true model-based approach, where a model is used to determine which areas on mask would benefit most from SRAFS and also to perform the initial SRAF placement. The model-based approach is particularly useful for random logic designs, where developing rules continues to be challenging.

For 20nm, the two key innovations in computational lithography involve enabling double patterning with concurrent OPC, and in improving difficult-to-print layouts with localized in-situ optimization and by using an inverse lithography technique.For 14nm, says Mentor Graphics’ OPC product marketing manager Gandharv Bhatara, computational lithography offers more tools for process window enhancement with better approaches to sub-resolution assist features (SRAFs). SRAFs have been used since the 130nm node for resolution enhancement, but for 14nm, SRAF placement has evolved considerably. In a recent article, Bhatara says that SRAF placement has moved from rules-based to model-based, and describes two new model-based approaches developed in the Mentor OPC tools. One approach uses inverse lithography (ILT) to create the golden reference for a rules-based SRAF placement. This gives superior process window for critical blocks like SRAM, where the rules are relatively easy to develop. The second approach is a true model-based approach, where a model is used to determine which areas on mask would benefit most from SRAFS and also to perform the initial SRAF placement. The model-based approach is particularly useful for random logic designs, where developing rules continues to be challenging.  Both methods are good, but for different design styles. Bhatara says that for 14nm, combining them into a hybrid approach provides a single, unified SRAF recipe for SRAM (rules-based) and random logic designs (model-based). So if you need the keys to 14nm computational lithography, look for advanced SRAF solutions that provide flexibility, control runtime, and leverage both rules-based and model-based approaches.You can find this and other content on foundry-based IC design and manufacturing at www.mentor.com/solutions/foundry.

Both methods are good, but for different design styles. Bhatara says that for 14nm, combining them into a hybrid approach provides a single, unified SRAF recipe for SRAM (rules-based) and random logic designs (model-based). So if you need the keys to 14nm computational lithography, look for advanced SRAF solutions that provide flexibility, control runtime, and leverage both rules-based and model-based approaches.You can find this and other content on foundry-based IC design and manufacturing at www.mentor.com/solutions/foundry.

Sponsor

Siemens Socials

Instance

Array

(

[node_name] => Siemens EDA

[node_id] => Array

(

[0] => 2

)

)

Nodes

XF\Mvc\Entity\ArrayCollection Object

(

[entities:protected] => Array

(

[367] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[title] => Siemens EDA

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 380

[display_in_list] => 1

[lft] => 81

[rgt] => 82

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[populated:protected] => 1

)

Threads

XF\Mvc\Entity\ArrayCollection Object

(

[entities:protected] => Array

(

[24826] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24826

[node_id] => 367

[title] => Siemens launches Teamcenter Digital Reality Viewer and Digital Twin Composer in India

[reply_count] => 0

[view_count] => 393

[user_id] => 25277

[username] => AmandaK

[post_date] => 1774391592

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98654

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1774391592

[last_post_id] => 98654

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 76

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[discussion_count] => 393

[message_count] => 396

[last_post_id] => 98654

[last_post_date] => 1774391592

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 24826

[last_thread_title] => Siemens launches Teamcenter Digital Reality Viewer and Digital Twin Composer in India

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"],"allow_answer_voting":false,"allow_answer_downvote":false}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[title] => Siemens EDA

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 380

[display_in_list] => 1

[lft] => 81

[rgt] => 82

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24825] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24825

[node_id] => 367

[title] => Siemens and Viakoo Collaborate to Deliver Advanced OT/IoT Security Management

[reply_count] => 0

[view_count] => 269

[user_id] => 25277

[username] => AmandaK

[post_date] => 1774391532

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98653

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1774391532

[last_post_id] => 98653

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 76

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[discussion_count] => 393

[message_count] => 396

[last_post_id] => 98654

[last_post_date] => 1774391592

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 24826

[last_thread_title] => Siemens launches Teamcenter Digital Reality Viewer and Digital Twin Composer in India

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"],"allow_answer_voting":false,"allow_answer_downvote":false}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[title] => Siemens EDA

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 380

[display_in_list] => 1

[lft] => 81

[rgt] => 82

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24824] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 57

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24824

[node_id] => 367

[title] => Siemens advances indoor air quality innovation through ARPA-H BREATHE projects

[reply_count] => 0

[view_count] => 131

[user_id] => 25277

[username] => AmandaK

[post_date] => 1774391494

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98652

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1774391494

[last_post_id] => 98652

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 76

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[discussion_count] => 393

[message_count] => 396

[last_post_id] => 98654

[last_post_date] => 1774391592

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 24826

[last_thread_title] => Siemens launches Teamcenter Digital Reality Viewer and Digital Twin Composer in India

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"],"allow_answer_voting":false,"allow_answer_downvote":false}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[title] => Siemens EDA

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 380

[display_in_list] => 1

[lft] => 81

[rgt] => 82

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24765] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 58

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24765

[node_id] => 367

[title] => Siemens Invests More Than $165 Million to Expand Manufacturing Across the Carolinas, Supporting U.S. Data Center Growth

[reply_count] => 0

[view_count] => 513

[user_id] => 25277

[username] => AmandaK

[post_date] => 1773817269

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98439

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1773817269

[last_post_id] => 98439

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 76

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[discussion_count] => 393

[message_count] => 396

[last_post_id] => 98654

[last_post_date] => 1774391592

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 24826

[last_thread_title] => Siemens launches Teamcenter Digital Reality Viewer and Digital Twin Composer in India

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"],"allow_answer_voting":false,"allow_answer_downvote":false}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[title] => Siemens EDA

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 380

[display_in_list] => 1

[lft] => 81

[rgt] => 82

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24764] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 59

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24764

[node_id] => 367

[title] => Siemens launches Fuse EDA AI Agent for automation across semiconductor, 3D IC and PCB system workflows

[reply_count] => 0

[view_count] => 442

[user_id] => 25277

[username] => AmandaK

[post_date] => 1773817223

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98438

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1773817223

[last_post_id] => 98438

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 76

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[discussion_count] => 393

[message_count] => 396

[last_post_id] => 98654

[last_post_date] => 1774391592

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 24826

[last_thread_title] => Siemens launches Teamcenter Digital Reality Viewer and Digital Twin Composer in India

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"],"allow_answer_voting":false,"allow_answer_downvote":false}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[title] => Siemens EDA

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 380

[display_in_list] => 1

[lft] => 81

[rgt] => 82

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24763] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 60

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24763

[node_id] => 367

[title] => Siemens Mitras manufacturing plant in Mexico earns LEED Platinum certification, becoming the first Siemens factory worldwide to achieve the highest...

[reply_count] => 0

[view_count] => 137

[user_id] => 25277

[username] => AmandaK

[post_date] => 1773817143

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98437

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1773817143

[last_post_id] => 98437

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 76

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[discussion_count] => 393

[message_count] => 396

[last_post_id] => 98654

[last_post_date] => 1774391592

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 24826

[last_thread_title] => Siemens launches Teamcenter Digital Reality Viewer and Digital Twin Composer in India

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"],"allow_answer_voting":false,"allow_answer_downvote":false}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[title] => Siemens EDA

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 380

[display_in_list] => 1

[lft] => 81

[rgt] => 82

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24762] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 61

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24762

[node_id] => 367

[title] => Introducing the new generation of logic controllers

[reply_count] => 0

[view_count] => 132

[user_id] => 25277

[username] => AmandaK

[post_date] => 1773817085

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98436

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1773817085

[last_post_id] => 98436

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 76

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[discussion_count] => 393

[message_count] => 396

[last_post_id] => 98654

[last_post_date] => 1774391592

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 24826

[last_thread_title] => Siemens launches Teamcenter Digital Reality Viewer and Digital Twin Composer in India

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"],"allow_answer_voting":false,"allow_answer_downvote":false}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[title] => Siemens EDA

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 380

[display_in_list] => 1

[lft] => 81

[rgt] => 82

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24761] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 62

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24761

[node_id] => 367

[title] => Siemens to help build AI-ready scientific infrastructure as part of U.S. Department of Energy’s Genesis Mission

[reply_count] => 0

[view_count] => 163

[user_id] => 25277

[username] => AmandaK

[post_date] => 1773817024

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98435

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1773817024

[last_post_id] => 98435

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 76

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[discussion_count] => 393

[message_count] => 396

[last_post_id] => 98654

[last_post_date] => 1774391592

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 24826

[last_thread_title] => Siemens launches Teamcenter Digital Reality Viewer and Digital Twin Composer in India

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"],"allow_answer_voting":false,"allow_answer_downvote":false}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[title] => Siemens EDA

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 380

[display_in_list] => 1

[lft] => 81

[rgt] => 82

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24666] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 63

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24666

[node_id] => 367

[title] => Inventec enhances server and notebook design for manufacturing excellence with Siemens’ software

[reply_count] => 0

[view_count] => 609

[user_id] => 25277

[username] => AmandaK

[post_date] => 1772665541

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98052

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1772665541

[last_post_id] => 98052

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 76

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[discussion_count] => 393

[message_count] => 396

[last_post_id] => 98654

[last_post_date] => 1774391592

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 24826

[last_thread_title] => Siemens launches Teamcenter Digital Reality Viewer and Digital Twin Composer in India

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"],"allow_answer_voting":false,"allow_answer_downvote":false}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[title] => Siemens EDA

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 380

[display_in_list] => 1

[lft] => 81

[rgt] => 82

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24645] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 64

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24645

[node_id] => 367

[title] => Siemens accelerates integrated circuit design and verification with agentic AI in Questa One

[reply_count] => 0

[view_count] => 349

[user_id] => 25277

[username] => AmandaK

[post_date] => 1772476157

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 97992

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1772476157

[last_post_id] => 97992

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 76

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[discussion_count] => 393

[message_count] => 396

[last_post_id] => 98654

[last_post_date] => 1774391592

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 24826

[last_thread_title] => Siemens launches Teamcenter Digital Reality Viewer and Digital Twin Composer in India

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"],"allow_answer_voting":false,"allow_answer_downvote":false}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[title] => Siemens EDA

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 380

[display_in_list] => 1

[lft] => 81

[rgt] => 82

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24644] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 65

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24644

[node_id] => 367

[title] => Siemens to deliver one of Australia’s largest cloud-based SCADA systems for renewable energy

[reply_count] => 0

[view_count] => 242

[user_id] => 25277

[username] => AmandaK

[post_date] => 1772476077

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 97991

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1772476077

[last_post_id] => 97991

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 76

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[discussion_count] => 393

[message_count] => 396

[last_post_id] => 98654

[last_post_date] => 1774391592

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 24826

[last_thread_title] => Siemens launches Teamcenter Digital Reality Viewer and Digital Twin Composer in India

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"],"allow_answer_voting":false,"allow_answer_downvote":false}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[title] => Siemens EDA

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 380

[display_in_list] => 1

[lft] => 81

[rgt] => 82

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24593] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 66

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24593

[node_id] => 367

[title] => Siemens wins Best of Show Award for “Packaging: Design” at 2026 Chiplet Summit

[reply_count] => 0

[view_count] => 608

[user_id] => 25277

[username] => AmandaK

[post_date] => 1771540072

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 97637

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1771540072

[last_post_id] => 97637

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 76

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[discussion_count] => 393

[message_count] => 396

[last_post_id] => 98654

[last_post_date] => 1774391592

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 24826

[last_thread_title] => Siemens launches Teamcenter Digital Reality Viewer and Digital Twin Composer in India

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"],"allow_answer_voting":false,"allow_answer_downvote":false}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[title] => Siemens EDA

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 380

[display_in_list] => 1

[lft] => 81

[rgt] => 82

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24592] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 67

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24592

[node_id] => 367

[title] => Siemens Foundation Launches Careers Electric™, a National Electrical Workforce Initiative

[reply_count] => 0

[view_count] => 480

[user_id] => 25277

[username] => AmandaK

[post_date] => 1771540026

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 97636

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1771540026

[last_post_id] => 97636

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 76

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[discussion_count] => 393

[message_count] => 396

[last_post_id] => 98654

[last_post_date] => 1774391592

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 24826

[last_thread_title] => Siemens launches Teamcenter Digital Reality Viewer and Digital Twin Composer in India

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"],"allow_answer_voting":false,"allow_answer_downvote":false}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[title] => Siemens EDA

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 380

[display_in_list] => 1

[lft] => 81

[rgt] => 82

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24591] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 68

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24591

[node_id] => 367

[title] => HD Hyundai selects Siemens Xcelerator for integrated digital shipbuilding platform

[reply_count] => 0

[view_count] => 432

[user_id] => 25277

[username] => AmandaK

[post_date] => 1771539914

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 97635

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1771539914

[last_post_id] => 97635

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 76

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[discussion_count] => 393

[message_count] => 396

[last_post_id] => 98654

[last_post_date] => 1774391592

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 24826

[last_thread_title] => Siemens launches Teamcenter Digital Reality Viewer and Digital Twin Composer in India

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"],"allow_answer_voting":false,"allow_answer_downvote":false}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[title] => Siemens EDA

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 380

[display_in_list] => 1

[lft] => 81

[rgt] => 82

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24490] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 69

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24490

[node_id] => 367

[title] => Siemens acquires Canopus AI to bring AI-based metrology to semiconductor manufacturing

[reply_count] => 0

[view_count] => 765

[user_id] => 25277

[username] => AmandaK

[post_date] => 1770240705

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 97182

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1770240705

[last_post_id] => 97182

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 76

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 367

[discussion_count] => 393

[message_count] => 396

[last_post_id] => 98654

[last_post_date] => 1774391592

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 24826

[last_thread_title] => Siemens launches Teamcenter Digital Reality Viewer and Digital Twin Composer in India

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>