Finding and debugging failures on integrated circuits has become increasingly difficult. Two sessions at ISTFA (International Symposium for Testing and Failure Analysis) on Thursday address the current best practices and research directions of diagnosis.

The first was a tutorial this morning by Mentor Graphics luminary Martin Keim on using scan diagnosis for failure analysis. Dr. Keim says the tutorial is both an introduction to diagnosis — describing what diagnosis actually is and what it can do for you, as well as practical advice to FA (failure analysis) folks how to make it work in their environment.

Defects, like death and taxes, are inevitable. Devices will fail because of manufacturing problems like contamination, insufficient doping, and process or mask errors. These problems cause shorts to power/ground, slow transistors, CMOS stuck-on/opens, and the like.

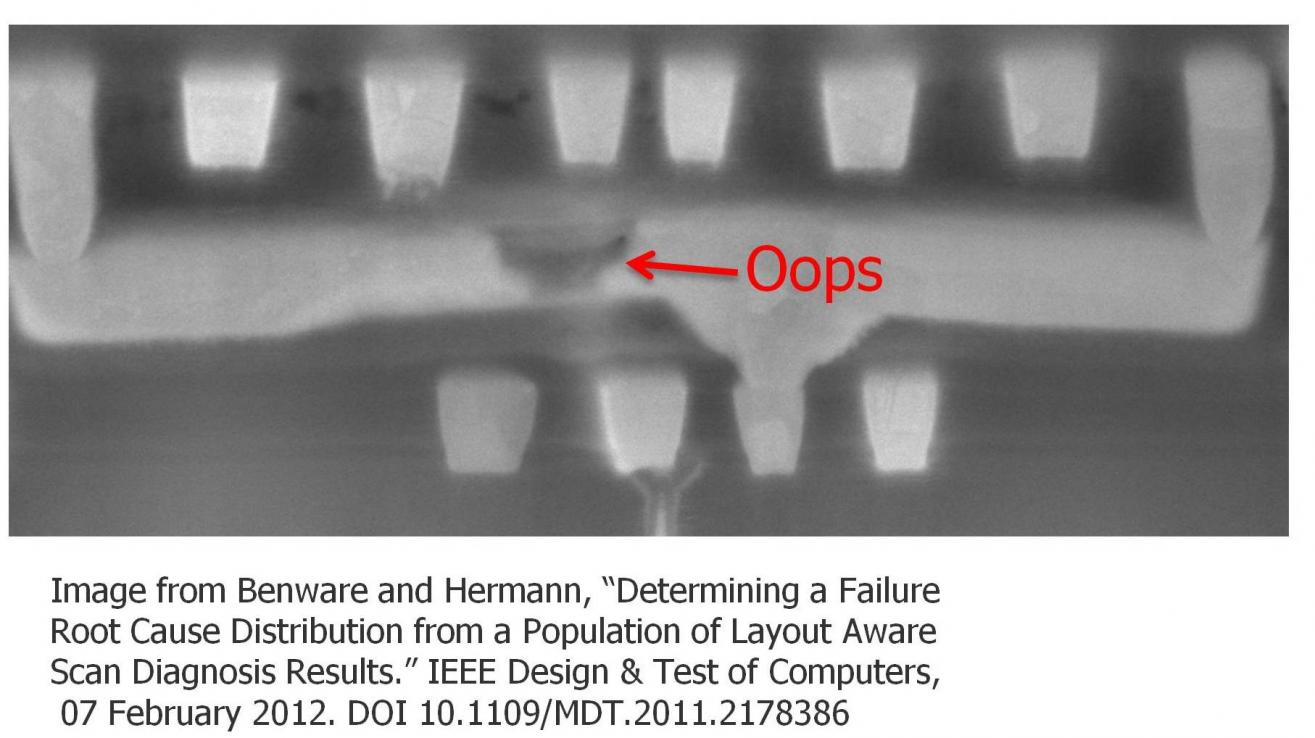

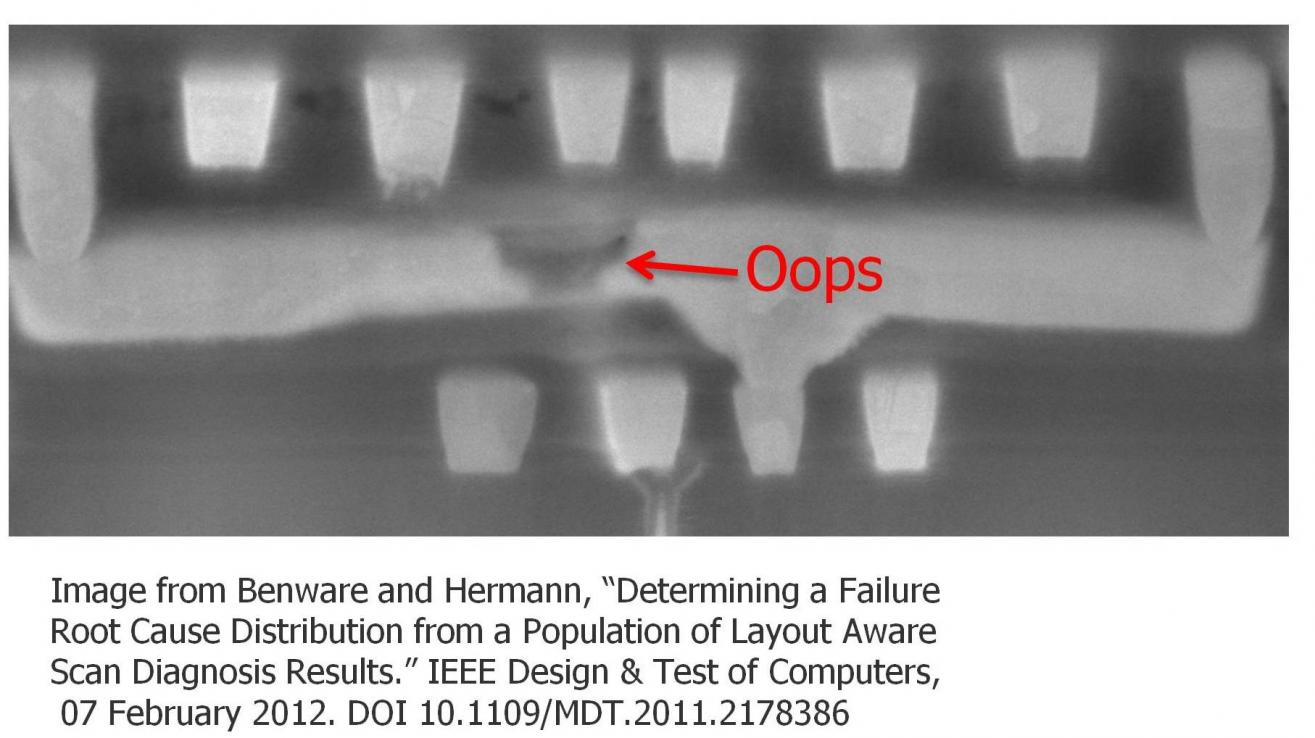

Faults are abstractions of physical defect behavior and can be represented as fault models in software and measured. Diagnosis tools (for example, ATPG) find faults; failure analysis tools finds defects. These two things work together. A diagnosis tool needs all the inputs and outputs of ATPG from the DFT engineers, and a datalog of failing devices from the test engineers. Okay, say you’ve got that managed and you run a diagnosis on a set of failed devices. The next thing to consider is the quality of the diagnosis results, and that depends in large part on the diagnosis tool you use. In particular, the tool should be layout-aware, as opposed to logic-only diagnosis. For details, you can download a whitepaper by Dr. Keim, Layout Aware Diagnosis. And for an industry case study perspective, look at the results of a diagnosis study between UMC, AMC, and Mentor in this paper available for a small cost through EDFAS.

For more views on test and diagnosis, you can attend a session of four papers (session 23) at a more reasonable hour on Thursday (3:25p-5:50p). The papers in this session address specific topics such as:

- Using diagnosis for failure localization and root cause analysis

- Leveraging test and characterization results in FA

- Test-for-yield

- Design-for-debug

- Linking design-for-test and CAD navigation

- Advances in diagnosis technology

- FA-optimized test and test equipment

- Industrial practices and new technologies

Troubleshooting how and why systems and circuits fail is important and is rapidly growing in industry significance. Debug and diagnosis may be needed for yield improvement, process monitoring, correcting the design function, failure-mode learning for R&D, or just getting a working first prototype. As you might imaging, this detective work is very tricky. Sources of difficulty include circuit and system complexity, packaging, limited physical access, shortened product creation cycle and time-to-market. These two ISTFA sessions are great sources of information on the new, efficient solutions for debug and diagnosis that have a much needed and highly visible impact on productivity.

Share this post via:

Comments

0 Replies to “Test and Diagnosis at ISTFA”

You must register or log in to view/post comments.