When I first started working in the semiconductor industry back in 1982, I realized that there was a race going on between the complexity of the system being designed and the capabilities of the technology in the tools and systems used to design them. The technology used to design the next generation of hardware was always lagging… Read More

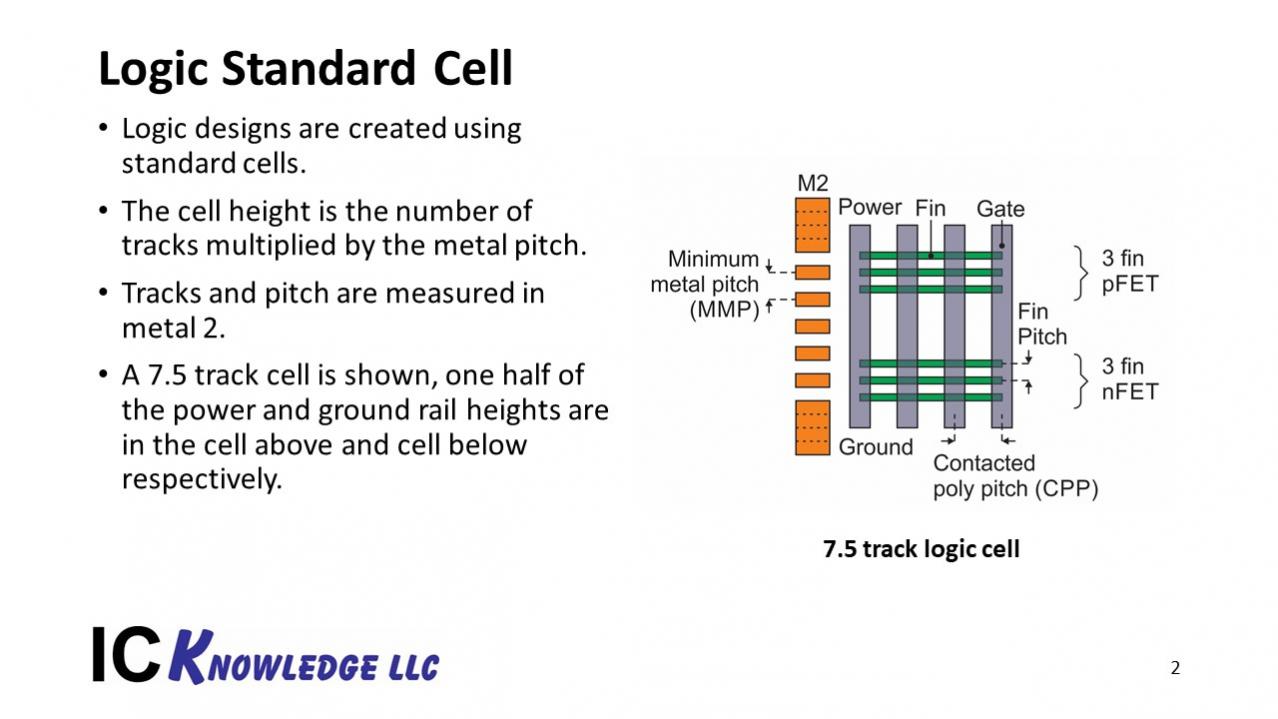

7nm, 5nm and 3nm Logic, current and projected processes

There has been a lot of new information available about the leading-edge logic processes lately. Papers from IEDM in December 2017, VLSIT this month, the TSMC and Samsung Foundry forums, etc. have all filled in a lot of information. In this article I will summarize what is currently known.… Read More

The Wolper Method

If you read around topics in advanced formal verification you’re likely to run into something called Wolper coloring, or what Vigyan Singhal (Chief Oski at Oski) calls the Wolper method. Many domains have specialized techniques but what’s surprising in this instance is a seeming absence of helpful on-line explanations (though… Read More

Billion Transistor Designs Need Faster Full Chip Tools

During the design cycle as tape out approaches, time pressure usually goes up dramatically. To make matters worse the design itself is much larger, because all the block level work is done and there is a requirement to work with the entire database. It feels like it’s time to put aside the garden trowel and start using a steam shovel.… Read More

Fractal Technologies Joins TSMC Open Innovation Platform EDA Alliance

In case you missed it, Fractal is now officially part of the TSMC EDA Alliance. Fractal Crossfire is the leading IP and Library QA tool used by TSMC and many of TSMC’s customers so this is for the greater IP good, absolutely. Fractal has also released a new white paper “Setup Generation for Fractal Crossfire” that we can talk about but… Read More

DRC is all About the Runset

EDA companies advertise their physical verification tools, aka DRC (Design Rule Check), mostly in terms of specific engine qualities such as capacity, performance and scalability. But they do not address an equally if not more important aspect: the correctness of the actual design rules.

Put bluntly: It’s not about how… Read More

Webinar: IP Quality is a VERY Serious Problem

We just completed a run through of the upcoming IP & Library QA webinar that I am moderating with Fractal and let me tell you it is a must see for management level Semiconductor Design and Semiconductor IP companies as well as the Foundries. Seriously, if you are an IP company you had better be up on the latest QA checks if you want … Read More

Webinar: RISC-V IoT Security IP

Disruptive technology and disruptive business models are the lifeblood of the semiconductor industry. My first disruptive experience was with Artisan Components in 1998. The semiconductor industry started cutting IP groups which resulted in a bubble of start-up IP companies including Artisan, Virage Logic, Aspec Technologies,… Read More

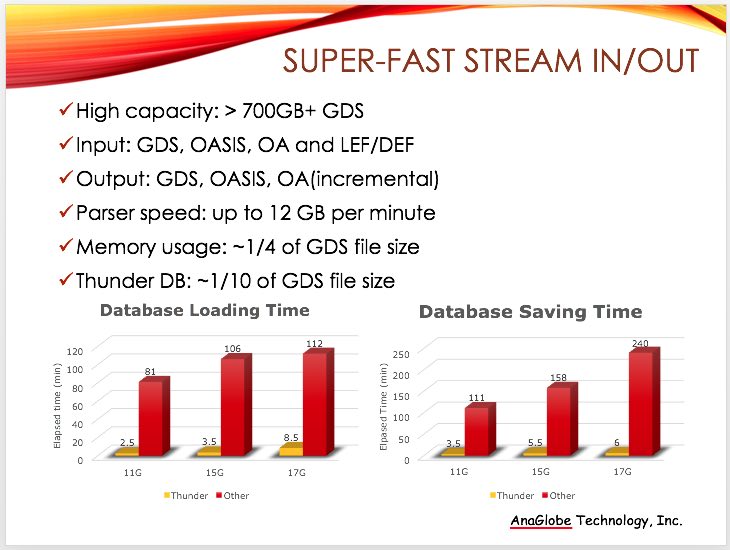

CEO Interview: YJ Su of Anaglobe

AnaGlobe Technology, Inc. is a leader in layout integration solutions that have been adopted by world-wide technology leading companies including the foundries, fabless, design services, packaging, panel, and IP companies. I know several of Anaglobe’s customers and am happy to work with them, absolutely.

The following… Read More

Worldwide Design IP Revenue Grew 12.4% in 2017

When starting SemiWiki we focused on three market segments: EDA, IP, and the Foundries. Founding SemiWiki bloggers Daniel Payne and Paul McLellan were popular EDA bloggers with their own sites and I blogged about the foundries so we were able to combine our blogs and hit the ground running. For IP I recruited Dr. Eric Esteve who had… Read More