I’ve been driving cars since 1975 and in the early days we had simplistic gauges for feedback like: Speed, Fuel level, Oil level, RPM. Back then when you popped the hood of a car you could see through the engine compartment onto the ground below, however with today’s cars the engine compartments are crammed with tubes,… Read More

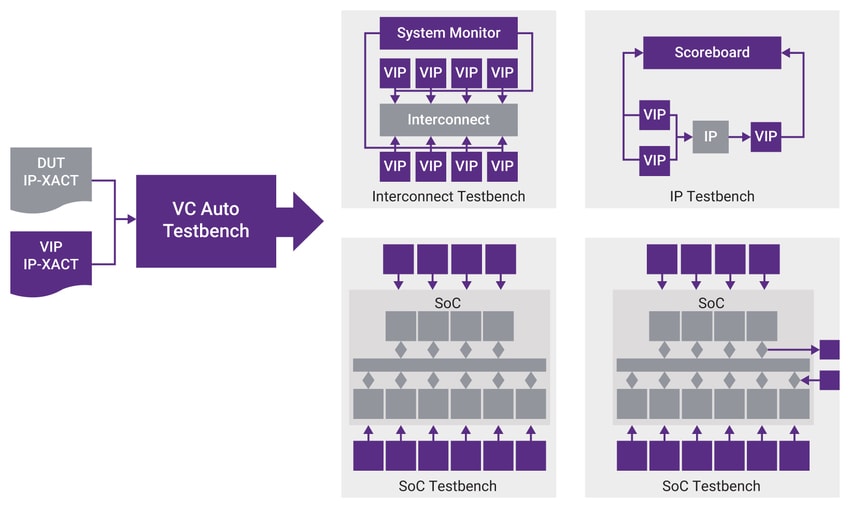

Webinar: Fast-track SoC Verification – Reduce time-to-first-test with Synopsys VC AutoTestbench

There seems to be a general sense that we have the foundations for block/IP verification more or less under control, thanks to UVM standardizing infrastructure for directed and constrained-random testing, along with class libraries providing building blocks to simplify verification reuse, build sequence tests, verify register… Read More

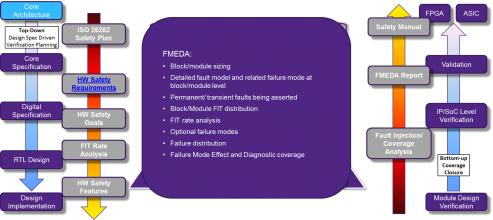

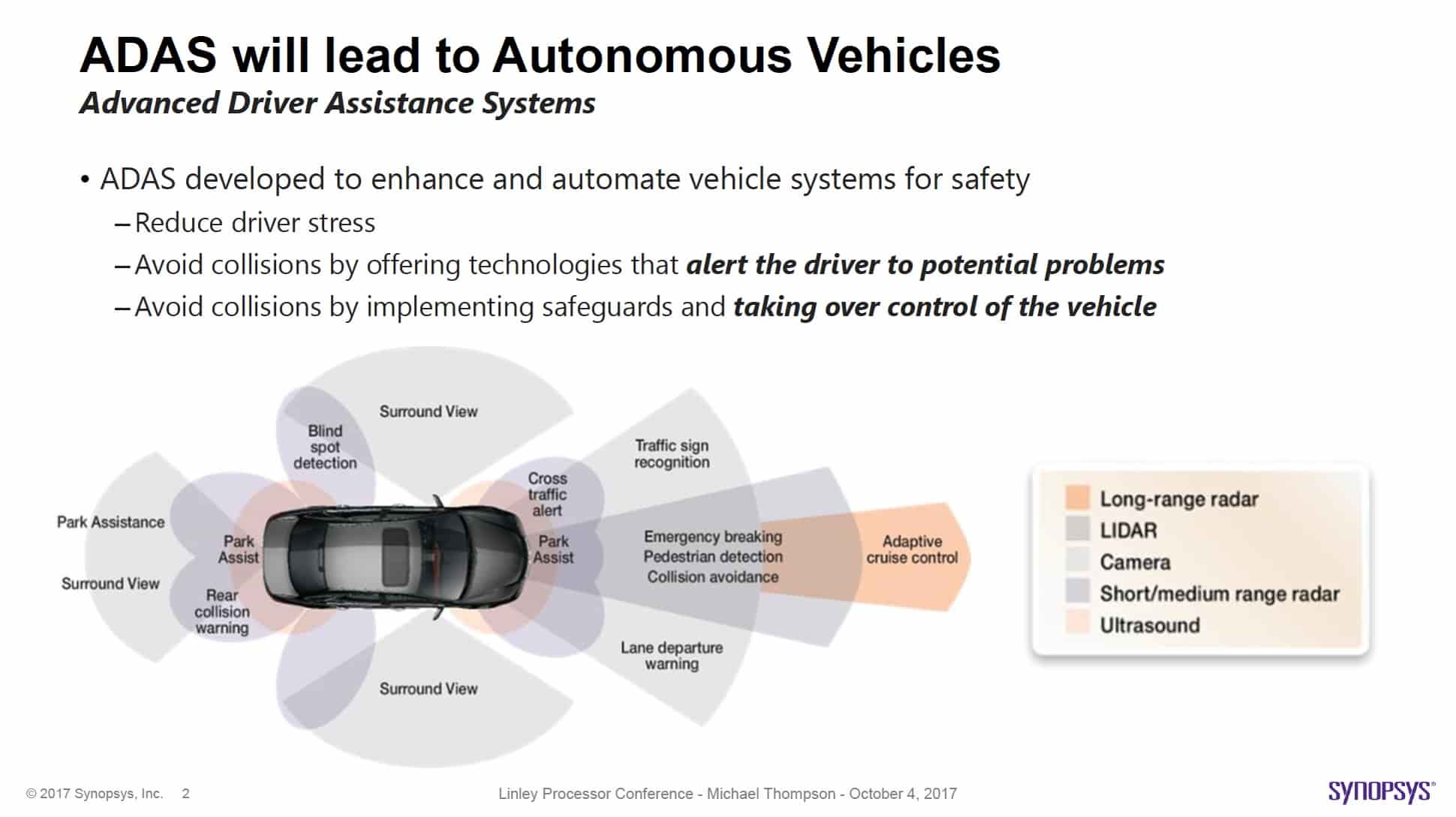

Achieving ISO 26262 Certification with ASIL Ready IP

According with McKinsey, “analysts predict revenue growth for advanced driver assistance systems (ADAS) to be up to 29 percent, giving the segment one of the highest growth rates in the automotive and related industries.” Design cycle in automotive segment is much longer than in segments like mobile, PC or consumer. If you expect… Read More

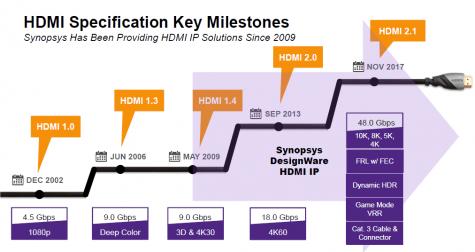

HDMI 2.1 Delivers 48.0 Gbps & Supports Dynamic HDR

You may or may not have bought HDMI-equipped device for black Friday or during year end break, but you TV set (or/and you PC) are certainly HDMI-powered, like the 750 million HDMI-equipped devices sold in 2016. In fact, cumulated shipment of HDMI-equipped devices has reached 6 BILLION since the protocol introduction in 2003! HDMI… Read More

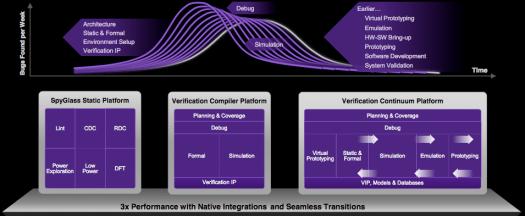

Shifting Left with Static and Formal Verification

Unless you have been living in a cave for the last several years, by now you know that “Shift Left” is a big priority in product design and delivery, and particularly in verification. Within the semiconductor industry I believe Intel coined this term as early as 2002, though it seems now to be popular throughout all forms of technology… Read More

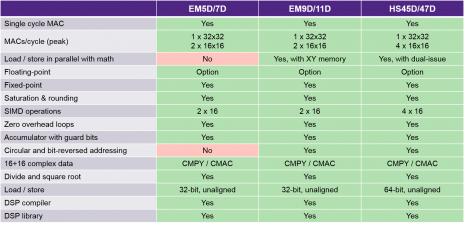

DSP Benchmarks and Libraries for ARC DSP families

Synopsys DesignWareARC HS4xD family is a perfect example of high performance DSP, enhanced RISC CPU IP core, able to address high-end IoT, mid to high-end audio or baseband control. ARC HS4xD architecture is 10-stage pipeline for high Fmax, resulting in excellent RISC efficiency with 5.2 CoreMark per MHz. ARC EMxD processors… Read More

Starblaze Uses Synopsys DesignWare IP to Launch SSD Controller SoC

I recently wrote an article about Synopsys’ DesignWare Security IP for the Internet-of-Things market and was interested to see that a startup, Starblaze Technology, has now used parts of the same IP in its latest Solid-State Drive (SSD) controller. The security IP caught my eye, but the rest of the story really put things into focus.… Read More

Synopsys White Paper on IoT Security – Introduces DesignWare Root-of-Trust Module

As the internet of things (IoT) continues its climb to a trillion devices, there has been many articles and books written on the need for securing those devices. With all the IoT gear that I seem to be picking up as Christmas presents, I feel like I’m doing my part to help the market get there, but I have to say, I sure hope the SoC designers… Read More

High performance processor IP targets automotive ISO 26262 applications

The reason you are seeing a lot more written about the ISO 26262 requirements for automotive electronics is, to put it bluntly, this stuff is getting real. Driver assist systems are no longer only found in the realm of Mercedes and Tesla, almost every car in every brand offers some driver assist features. However, the heavy lifting… Read More

VESA DSC Encoder Enables MIPI DSI to Support 4K resolutions

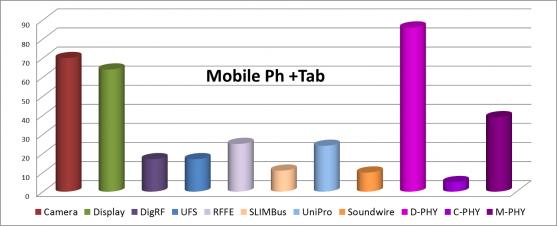

Some of the MIPI specifications are now massively used in mobile (smartphone), like the Multimedia related specs, Camera Serial Interface (CSI-2) and Display Serial Interface (DSI). These specifications are now adopted inautomotive infotainment systems, and augmented reality (AR)/ virtual reality (VR) devices. If you … Read More