Synopsys runs a “Industry verifies with Synopsys” lunch at each DVCon, which isn’t as cheesy as the title might suggest. The bulk of the lunch covers user presentations on their use of Synopsys tools which I find informative and quite open, sharing problems as much as successes. This year, Eamonn Quiqley, FPGA engineering manager… Read More

Synopsys Tackles Debug for Giga-Runs on Giga-Designs

I think Synopsys would agree that they were not an early entrant to the emulation game, but once they really got moving, they’ve been working hard to catch up and even overtake in some areas. A recent webinar highlighted work they have been doing to overcome a common challenge in this area. Being able to boot a billion-gate design, … Read More

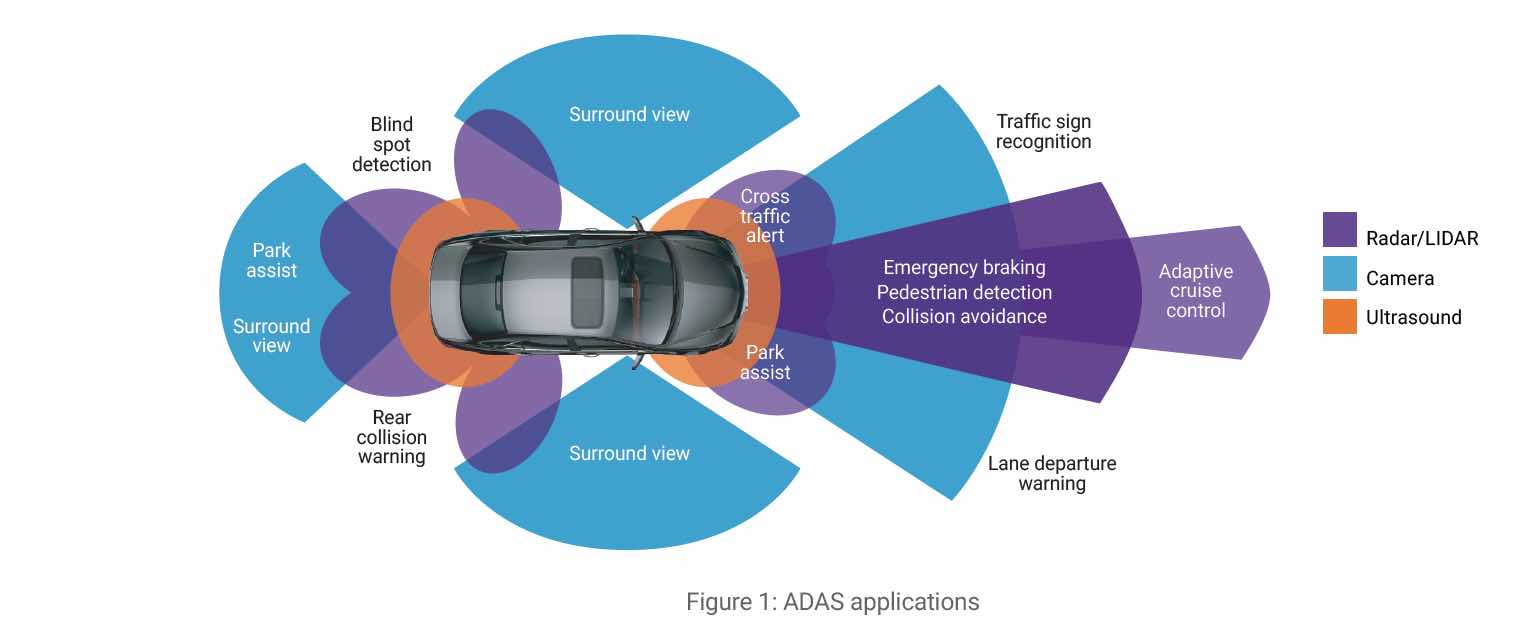

Accelerating SOC Development for Automobile Applications

No area of electronics is moving faster than automotive semiconductors. Everyone has been talking about the increasing electronics content of automobiles for decades. With Advanced Driver Assistance System (ADAS) and autonomous driving becoming a reality the pace has picked up even more. These new designs combine just about… Read More

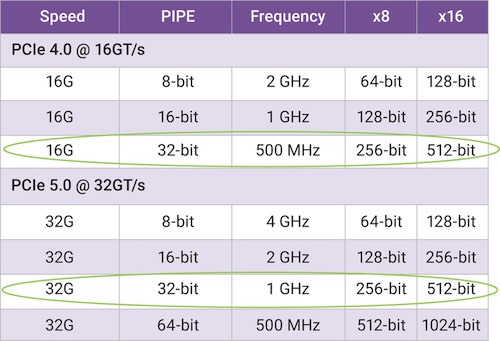

PCIe 5.0 Jumps to the Fore in 2019

2019 will be a big year for PCIe. With the approval of version 0.9 of the Base Layer for PCIe 5.0, implementers have a solid foundation to begin working on designs. PCIe 4.0 was introduced in 2017, before that the previous PCIe 3.0 was introduced in 2010 – ages ago in this industry. In fact, 5.0 is so close on the heels of 4.0, many products… Read More

Synopsys GLOBALFOUNDRIES and Automotive IP

IP vendors have always had the inside track on the status of new process nodes and what customers are planning for their next designs. This is even more apparent now that systems companies are successfully doing their own chips by leveraging the massive amounts of commercial IP available today. Proving once again that IP really … Read More

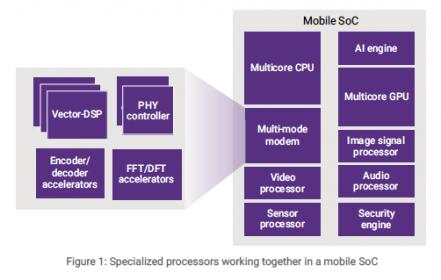

Goldilocks Solution for SOC Processors

SOC designers face choices when it comes to choosing how to implement algorithms in their designs. Moving them to hardware usually offers advantages of smaller area, less power and faster processing. Witness the migration of block chain hashing from CPUs to ASICs. However, these advantages can come with trade-offs. For one, … Read More

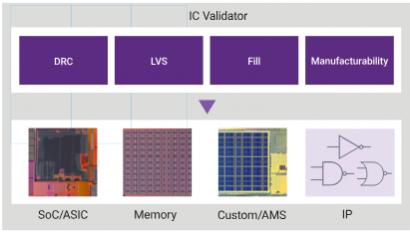

Switch Design Signoff with IC Validator

The surge of network traffic at the data centers has driven to an increase in network bandwidth, doubling every 12-15 months according to a study conducted on Google’s data centers. The primary drivers to this uptick include the proliferation of cloud computing, more distributed storage architecture, emerging applications… Read More

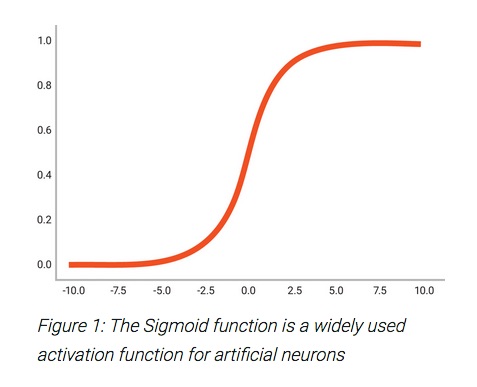

Mathematics are Hard – That is Why AI Needs Mathematics Hardware

The field of artificial intelligence has relied on heavy inspiration from the world of natural intelligence, such as the human mind, to build working systems that can learn and act on new information based on that learning. In natural networks, neurons do the work, deciding when to fire based on huge numbers of inputs. The relationship… Read More

Physical Verification with IC Validator

If a picture worths a thousand words, a tapeout quality SoC design with billions of polygons would compose a good book. To proofread this final design transformation format requires a foundry driven DRC/LVS signoff solution that nowadays is becoming more complex with further process scaling and shrinking pitch dimension.

Despite… Read More

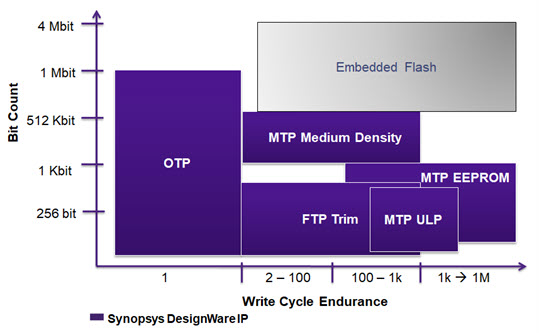

Synopsys Offers Smooth Sailing for OTP NVM

Nobody likes drama. Wait, let me narrow that down a bit. Chip designers really hate drama. They live in a world of risk and uncertainty, a world that tool and IP vendors spend considerable resources trying to make safer and more rational. It’s notable just how ironic that Sidense and Kilopass were duking out patent litigation in the… Read More