At ARM TechCon this year, the company announced the Neoverse brand targeted to infrastructure, contrasting with the Cortex brand we are familiar with for edge devices such as smartphones and IoT devices. Cortex was already used in infrastructure, in networking, base stations and the like but Neoverse splits the infrastructure… Read More

Semiconductor Intellectual Property

Imperas and RISC-V

I met Imperas at TechCon this year because I wanted to become a bit more knowledgeable about virtual modeling. That led me to become more interested in RISC-V and a talk given by Krste Asanovic of UCB and SiFive. My takeaway surprised me. I had thought this was an open-source David versus proprietary Goliaths (Intel and ARM) battle… Read More

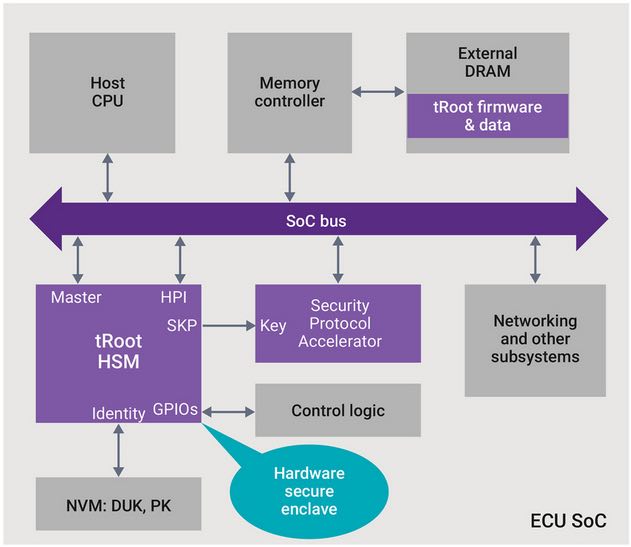

Car Vandals Eschew Crowbars

It used to be that automotive theft and crime was perpetrated with a crowbar. Now with increased electronics content, car designer and owners need to worry about electronic threats. Anywhere there is a communication link or a processor, there are potential threats to the security of the car. The range of these threats covers everything… Read More

Webinar: Turnkey Bluetooth True Wireless Stereo Earbuds and Speakers

When we were first introduced to earbuds, in-ear speakers connected through thin wires to your phone (and earlier portable music devices), they seemed pretty convenient for private entertainment at work, while walking, exercising, doing almost anything. Until we started to realize those long dangly wires weren’t ideal. They’d… Read More

RISC-V End to End Solutions for HPC and Networking

Semiconductor IP is one of the more exciting and most viewed topics we cover on SemiWiki, it has been that way since we began in 2011 and that trend will continue indefinitely, my opinion.

Semiconductor IP: Total Blogs: 640: Total Views: 3253751: Average: 5084

Based on the design starts we track, Cloud Computing is a leading semiconductor… Read More

Security and RISC-V

One of the challenges in the RISC-V bid for world domination may be security. That may seem like a silly statement, given that security weaknesses are invariably a function of implementation and RISC-V doesn’t define implementation, only the instruction-set architecture (ISA). But bear with me. RISC-V success depends heavily… Read More

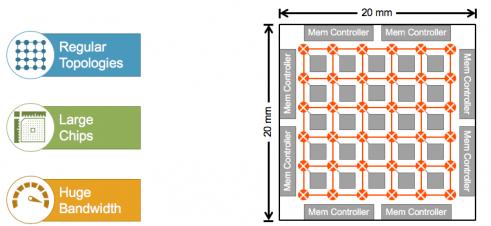

On-Chip Networks at the Bleeding Edge of ML

I wrote a while back about some of the more exotic architectures for machine learning (ML), especially for neural net (NN) training in the data center but also in some edge applications. In less hairy applications, we’re used to seeing CPU-based NNs at the low end, GPUs most commonly (and most widely known) in data centers as the workhorse… Read More

Is IP SoC 2018 Still Alive? Better than Ever!

The 21[SUP]st[/SUP] IP-SoC Days conference will be held in Grenoble, France, on December 5-6, 2018. IP-SoC is now the unique IP centric conference, with presentations reflecting the complete IP ecosystem: IP suppliers and foundries, external IP or internal reuse managers. Look at the program, you will see the hot topics covered… Read More

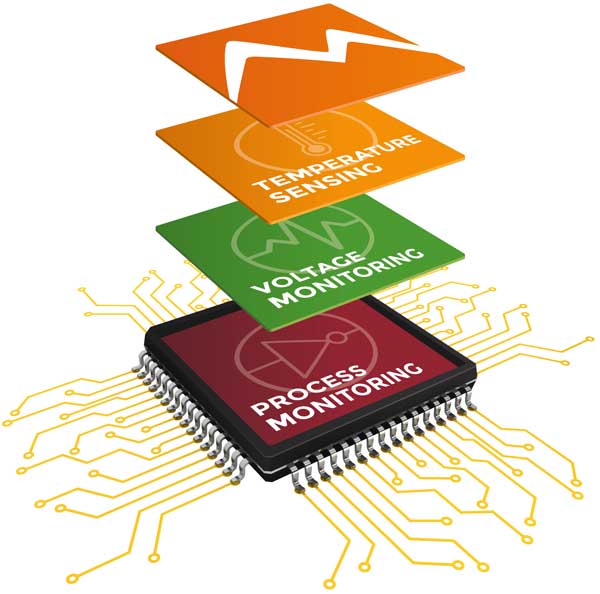

Making AI Silicon Smart with PVT Monitoring

PVT – depending on what field you are in those three letters may mean totally different things. In my undergraduate field of study, chemistry, PVT meant Pressure, Volume & Temperature. Many of you probably remember PV=nRT, the dreaded ideal gas law. However, anybody working in semiconductors knows that PVT stands … Read More

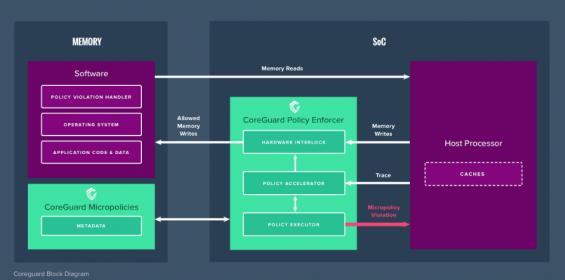

Dover Microsystems Spins New Approach to Security

One of the companies I met at ARM TechCon was Dover Microsystems who offer a product in embedded security. You might ask why we need yet another security solution. Surely we’re overloaded with security options from ARM and many others in the forms of TEEs, secure boots, secure enclaves and so on? Why do we need more? Because defending… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era