I met Mike Sanie around DVCon time and planned to write a blog about the one year anniversary of Synopsys Discovery VIP which was announced during Aart’s keynote at DVCon in 2012. Eric covered it for SemiWiki here. But Synopsys had other stuff they wanted me to blog about and so it is a couple of months late. The 14th month anniversary… Read More

Semiconductor Intellectual Property

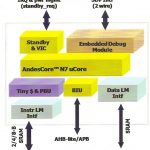

Andes, ARM, Imagination, MIPS

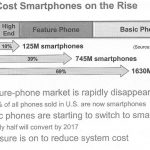

The last session of the day for Linley Mobile was about processors to go into smartphones. One surprise was that there is a core that nobody seems to have heard of since it is only really used in Taiwan up until now, and it is used in several Mediatek chips.

The most “glamorous” processor in a smartphone is the one in the application… Read More

Linley Mobile

I was at the Linley Mobile Microprocessor conference earlier in the week. Well, just the first day since the second day overlapped with the GSA Silicon Summit. The first surprise was seeing Mike Demler in a suit. It turns out that he has joined the Linley Group as a full-time analyst in the mobile space.

Linley Gwennap started the day… Read More

On Resistive RAM Product Announcements and Meetings

A lot has been happening in the ReRAM world over the past couple of months. At the ISSCC Conference in February Toshiba/SanDisk presented a paper describing a 32Gbit ReRAM chip.… Read More

Using Android Multimedia Framework drastically reduces power consumption in mobile

The multiplication of chips capable to run Multimedia processing (sound, image or video) in a mobile device, smartphone or media tablet, like Application Processor (AP), Baseband (BB), Codec or companion chip, each of these embedding one or multiple processor can be seen as a good opportunity to simplify the device architecture…… Read More

Prediction is very difficult… is it a reason for writing down everything that springs to mind?

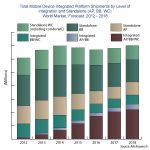

Smartphone and Media tablet markets are exploding, generating huge level of profit for the Apple, Samsung or Qualcomm, and we don’t see yet when the growth will stop. That’s a point. But is it a reason for analyst to write down everything that springs to mind, including obvious insanity? Let’s have a look at the diagram below, and … Read More

Kilopass Sidense Legal Battle

The decision made by United States Court of Appeals for the Federal Circuit, “Affirming” the District Court for the Northern District of California’s summary judgment of non-infringement on Kilopass’ patent claims and its dismissal, with prejudice, of all remaining claims against Sidense, is certainly a good news for IP and… Read More

Denali+Tensilica+Cosmic = Cadence

I won’t be able to attend Chris Rowen’s presentation here at the GlobalPress Electronic Summit since I’m going to the first day of the Linley Mobile Microprocessor conference. In fact I wonder if Chris himself will make it since he was running in the Boston marathon on Monday. He finished about 10 minutes before… Read More

Cavendish Kinetics

I have spent the last couple of days at the GlobalPress Electronics Summit at the Chaminade Resort in Santa Cruz. Hey, it’s tough, but someone has to do it. One interesting presentation was from Cavendish Kinetics. It is especially interesting because many years ago Cavendish was founded by Mike Beunder, who I know well since… Read More

Altera, Intel, TSMC, ARM: the Plot Thickens

Vince Hu of Altera presented us her at the GlobalPress Electronics Summit on their process roadmap. Since just a month or two ago they announced that Intel would be their foundry at 14nm, everyone wanted to get a better idea of what was really going on.

At 28nm, Altera use 2 processes, TSMC 28HP (for high end Stratix-5 devices) and TSMC… Read More

TSMC N3 Process Technology Wiki