You could be forgiven for thinking that wireless in an IoT device must be Bluetooth-5 or Zigbee or Thread. After all, that’s what ARM has introduced as a part of their IoT solution and they have market weight that is difficult to dismiss. However those options aren’t the only game in town. There is already some level of (second… Read More

Semiconductor Intellectual Property

Flex Logix is a Different Kind of IP Company!

The embedded FPGA business has been getting quite a bit of press lately so it is definitely worth a closer look. Intel started it all when they acquired the #2 FPGA company Altera for $16.7B last year. Microsoft is also a big FPGA fan for search and deep learning. In fact, Microsoft’s commitment to FPGAs, specifically Altera FPGAs,… Read More

Performance Analysis for ARM Based SOC’s

ARM estimates that many SOC’s designed today have over 200 IP components. This statistic comes from a recent white paper ARM published addressing the topic of system performance analysis. This number is only going to go up. According the ARM this creates a huge challenge in ensuring the system is designed with adequate performance… Read More

Designing for Ultra-Low Power? Easier with “CLICK” IP

Designing for ultra-low power will become the mantra for many of the new SoC designs, but the related SoC architecture can be very complex to handle. Make or buy is the project manager choice, but if you decide to ask for an expert advice before jumping start an ULP SoC design, attending thiswebinar from Dolphin Integration “The Proven… Read More

Webinar: ARM Security Solution for IoT

Yossi Weisblum will be presenting ARM’s IoT security solution during the Open Silicon webinar that I am moderating next week. Yossi manages product marketing for ARM’s CryptoCell subsystem. He has an extensive background in product marketing across several platforms, including connectivity, wireless, multimedia and mobile.… Read More

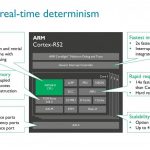

ARM and Mentor talk about Real Time Virtualization, Webinar

Processor cores come in a wide variety of speeds, performance and capabilities, so it may take you some time to find the proper processor for your system. Let’s say that you are designing a product for the industrial, automotive, military or medical markets that has an inherent requirement for safety, security and reliability… Read More

Design for Ultra-Low Power LTE: CEVA Webinar

You might have thought that ultra-low power communication for the IoT was limited to standards like BT5 and 802.15.4 (eg in ZigBee and Thread) which depend on gateways to cellular networks and limit reach, especially deep inside buildings. But now there’s a new standard for ultra-low power and ultra-low cost based on LTE, known… Read More

CEO Interview: Randy Caplan of Silicon Creations

For the next installment in our series of semiconductor CEO interviews we meet with Randy Caplan from Silicon Creations. Randy has helped build the company from a small startup to one of the world’s leading providers of interface and clocking IP. Almost every new chip developed these days has a requirement for PLLs and SerDes. Since… Read More

ISO 9001:2015 – Not Just for the Big Guys

If you are like me, you remember the banners that large companies put up years ago when they achieved ISO 9001 compliance. It seemed at the time that this was something only for large companies. Since its introduction in 1987 ISO 9001 has both evolved as a standard and has become an achievement that not just large manufacturing companies… Read More

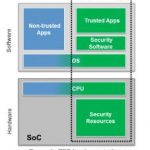

How to Secure a SoC while Keeping Area and Power Competitive?

I have attended LETI conference last June and remember the paper presented by Alain Merle, their security guru. Alain said that smart cards are secured because up to 50% of the Silicon area is dedicated to security. When you design a SoC to address applications like smart metering, NFC payment or embedded SIM, you know in advance … Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era