When I had to define the various IP categories (processor, analog & mixed-signal, wired interfaces, etc.) to build the Design IP Report, I scratched my head for a while about the processor main category: how to define the sub-categories? Not that long ago, it was easy to identify a CPU IP core and a DSP IP core. As of today, if a DSP… Read More

Semiconductor Intellectual Property

Embedded FPGA IP update — 2nd generation architecture, TSMC 16FFC, and a growing customer base

Regular Semiwiki readers are aware that embedded FPGA (eFPGA) IP development is a rapidly growing (and evolving) technical area. The applications for customizable and upgradeable logic in the field are many and diverse — as a result, improved performance, greater configurable logic capacity/density, and comprehensive… Read More

Understanding Sources of Clock Jitter Critical for SOC’s

Jitter issues in SOC’s reside at the crossroads of analog and digital design. Digital designers would prefer to live in a world of clocks that are free from jitter effects. At the same time, analog designers can build PLL’s that are precise and finely tuned. However, when a perfectly working PLL is inserted into an SOC, things can … Read More

The eFPGA Market is Heating Up!

It is nice to see an emerging market successfully emerge for a change. With embedded FPGAs we are way past test chips and are now seeing tape-outs and silicon in a variety of applications. I’m not sure what the current market estimate of eFPGA is just yet but they align nicely with the $30B+ micro controller market. Market studies have… Read More

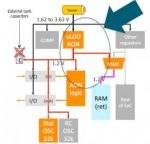

Webinar: Recipe to consume less than 0.5 µA in sleep mode

Dolphin is addressing the ultra-low-power (ULP) needs for some applications, like for example Bluetooth low energy (BLE), machine-to-machine (M2M) or IoT edge devices in general. For these applications, defining active and sleep modes is imperative, but it may not be enough to guarantee that the battery-powered system will… Read More

Webinar – Voice Interfaces of the Future

In our favorite Sci-Fi or fantasy movies or series we routinely expect voice-control of the many devices encountered in those stories. This seems natural because that’s how we most easily communicate our needs and intent (short of direct brain connections, though Elon Musk is apparently working on that). Typing on a keyboard … Read More

Building Better Digital Content Protection

Back in college my roommates figured out that the TV cable coax wire was still connected to our apartment. As a result, I was able to watch the Richard Pryor movie Silver Streak about 30 times without a cable box, however the screen was partially jumbled from the simple content protection used back then. This was possible by aggressively… Read More

CEO Interview: Vincent Markus of Menta

What is Menta all about?

Menta was founded to add hardware-programmability within SoCs. We deliver FPGAs in hard IP form that can be readily embedded within an SoC to make certain hardware functions reconfigurable at-will, post-production. This enables customers to dynamically adapt to evolving standards, perform security… Read More

ARM’s (Back!) in FD-SOI. NXP’s Showing (Real!) Chips.

“Yes, we’re back,” Ron Moore, VP of ARM’s physical design group told a packed ballroom at the recent FD-SOI Symposium organized in Silicon Valley by the SOI Consortium. FD-SOI gives you a silicon platform that’s highly controllable, enables ultra-low power devices, and is really good with RF, said Ron Moore during his presentation,… Read More

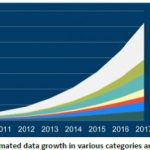

Data Center Explosion Push for Fast Adoption of 25G

The data center rack server market is estimated to growat a high Compound Annual Growth Rate (CAGR) of 20% to reach $90 billion by 2021. Such growth is due to the significantly rise in the number of connected devices, the growth in the volume of data per device and theneed for quick processing of high-volume data. Much of these data … Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era