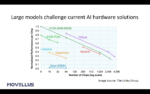

We are currently in the hockey stick growth phase of AI. Advances in artificial intelligence (AI) are happening at a lightning pace. And, while the rate of adoption is exploding, so is model size. Over the past couple of years, we’ve gone from about two billion parameters to Google Brain’s recently announced trillion-parameter… Read More

Tensilica Edge Advances at Linley

The Linley spring conference this year had a significant focus on AI at the edge, with all that implies. Low power/energy is a key consideration, though increasing performance demands for some applications are making this more challenging. David Bell (Product Marketing at Tensilica, Cadence) presented the Tensilica NNE110… Read More

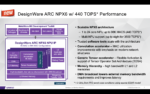

Bigger, Faster and Better AI: Synopsys NPUs

AI-based applications are fast advancing with evolving neural network (NN) models, pushing aggressive performance envelopes. Just a few years ago, performance requirements of NN driven applications were at 1 TOPS and less. Current and future applications in the areas of augmented reality (AR), surveillance, high-end smartphones,… Read More

Future.HPC is Coming!

According to the experts, the semiconductor industry is poised for a decade of growth and is projected to become a trillion dollar industry by 2030. In 2021 the semiconductor industry finally hit $600B so $1T by 2030 seems like a big ask, but not really if you look at the indicators inside the semiconductor ecosystem. Foundries, … Read More

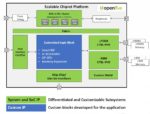

IP Subsystems and Chiplets for Edge and AI Accelerators

From a business viewpoint we often read in the technical press about the virtues of applying AI, and in the early days most of the AI model building was done in the cloud, because of the high computation requirements, yet there’s a developing trend now to use AI accelerators at the Edge. The other mega-trend in the past decade… Read More

High Efficiency Edge Vision Processing Based on Dynamically Reconfigurable TPU Technology

While many tough problems relating to computing have been solved over the years, vision processing is still challenging in many ways. Cheng Wang, Co-Founder and CTO of FlexLogix Technologies gave a talk on the topic of edge vision processing at Linley’s Spring 2022 conference. During that talk he references how Gerald Sussman… Read More

The Path Towards Automation of Analog Design

You may have noticed that I have been writing a lot more about analog design lately. This is no accident. Analog and custom blocks are increasingly important because of the critical role they play in enabling many classes of systems, such as automotive, networking, wireless, mobile, cloud, etc. Many of the SoCs needed for these… Read More

Bespoke Silicon is Coming, Absolutely!

It was nice to be at a live conference again. DesignCon was held at the Santa Clara Convention Center, my favorite location, which to me there was a back to normal crowd. The sessions I attended were full and the show floor was busy. Masks and vaccinations were not required, maybe that was it. Or there was a pent-up demand to get back engaged… Read More

The Lost Opportunity for 450mm

I spent several days this week at the SEMI International Strategy Symposium (ISS). One of the talks was “Can the Semiconductor Industry Reach $1T by 2030” given by Bob Johnson of Gartner. His conclusion was, that $1 trillion dollars is an aggressive forecast for 2030 but certainly we should reach $1 trillion dollars in the next 10… Read More

5G Core – Building An Open, Multi-Vendor Ecosystem

For those not familiar with Fierce Technology, this firm offers a one stop place for news, analysis and education in the areas of telecom, wireless, sensors and all related electronics markets. They organize popular events such as the 5G Blitz Week, Sensors Innovation Week series, Sensors Converge and many more. These events … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center