In this era of high-performance, low-power, and low-cost devices coming up at an unprecedented scale, the SoCs can never attain the ultimate in performance; always there is scope for improvement. Several methods including innovative technology, multi-processor architecture, memory, data traffic management for low latency,… Read More

5 ways FPGA-based prototyping shrinks design time

Engineers are trained to think linearly, along the lines of we started here, then we did this, and that, and this other stuff, and here is where we ended up. If you’ve ever presented in an internal review meeting, sales conference, or a TED-like event, you know that is a dangerous strategy in winning friends and influencing people.… Read More

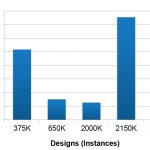

HiSilicon’s Experience with Synopsys ICC2

At TSMC’s OIP Symposium last month, Zhe (Jared) Lui of HiSilicon presented their experiences with Synopsys’ ICC2 physical design suite.

Jared started by giving an overview of Huawei and HiSilicon. HiSilicon is the semiconductor arm of Huawei. I assume everyone knows who Huawei is. To a first approximation they … Read More

Perfecting the Great Verification Fugue

Michael Sanie (Senior Director Marketing in the Synopsys Verification Group) gave the wrap-up presentation at SpyGlass World recently, on the Synopsys Verification Direction. I learned from an interview Michael gave to Paul McLellan that he is an accomplished pianist. I’m a pianist also, though of considerably less talent,… Read More

SpyGlass World 2015 User Group Meeting

I attended SpyGlass World this week – to give you an update, to catch up with old friends, including users, and to meet some of the new (to me) players from the Synopsys side of the event. The event was held in the United Club at Levi stadium, just like last year. Don’t know if this will continue. Merging the SpyGlass User Group into SNUG… Read More

Three New Things from ITC this year

The NFL has its annual Super Bowl contest each year, EDA vendors attend DAC, then the test folks attend ITCwhich was in Anaheim a few weeks ago. I’ve marketed ATGP, BIST and DFT tools before so I like to keep updated on what’s happening at conferences like ITC. Robert Ruiz from Synopsys spoke with me by phone to provide … Read More

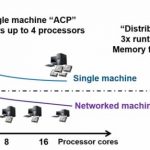

Why FPGA synthesis with Synplify is now faster

The headline of the latest Synopsys press release drops quite a tease: the newest release of Synplify delivers up to 3x faster runtime performance in FPGA synthesis. In our briefing for this post, we uncovered the surprising reason why – and it’s not found in their press release.… Read More

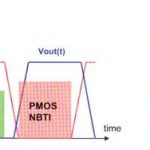

FinFET Reliability Analysis with Device Self-Heating

At the recent TSMC OIP symposium, a collaborative presentation by Synopsys and Xilinx highlighted the importance of incorporating the local FinFET device self-heating temperature increase on the acceleration of device reliability mechanisms.… Read More

SpyGlass World at Levi Stadium, October 21st

I suppose you might have something better to do next Wednesday but, seriously, it had better be pretty good. I admit I’m biased (I was the Atrenta CTO until very recently) but even given that and mixing metaphors, Atrenta really knocked it out of the park when they got the 49er stadium for their User Group meetings. You don’t have to … Read More

Leveraging Synopsys’ Lynx Design System for SoC Designs on Advanced Nodes

There was a time when design goals were decided in the beginning, targeted on a particular technology node, design planning done for the same, and implementation done through point tools connected indesign flows customized according to the design. It’s no longer the case for modern SoC designs; there are multiple technology … Read More