You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 14

[name] => Synopsys

[slug] => synopsys

[term_group] => 0

[term_taxonomy_id] => 14

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 791

[filter] => raw

[cat_ID] => 14

[category_count] => 791

[category_description] =>

[cat_name] => Synopsys

[category_nicename] => synopsys

[category_parent] => 157

[is_post] =>

)

WP_Term Object

(

[term_id] => 14

[name] => Synopsys

[slug] => synopsys

[term_group] => 0

[term_taxonomy_id] => 14

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 791

[filter] => raw

[cat_ID] => 14

[category_count] => 791

[category_description] =>

[cat_name] => Synopsys

[category_nicename] => synopsys

[category_parent] => 157

[is_post] =>

)

With the announcement of early PDK availability for the 3nm GAA process node, designers are extremely interested in the characteristics of the new “gate-all-around” transistor structure and how it compares to the existing FinFET device. The GAA transistor has been denoted as a (horizontal) nanowire or nanosheet.

I will talk… Read More

SLM. It’s a TLA (three-letter acronym) that you’ll be hearing more about. It stands for silicon lifecycle management and it has the potential of re-defining the role of EDA in the entire electronics ecosystem. A working definition of SLM is “monitoring, analysis and optimization of semiconductor devices as they are designed,… Read More

Anyone who frequents SemiWiki will likely know Moore’s Law. The prediction made by Gordon Moore over 50 years ago regarding the relentless increase in transistor density and reduction in cost has tracked well for a very, very long time. In recent years, there has been spirited discussion about the end of Moore’s Law. This is a discussion… Read More

Virtual events are coming fast and furious. Even though we are sheltering there is still the need to pick and choose carefully because time really is big money inside the semiconductor design ecosystem, absolutely.

Synopsys virtual events are high on my list for three reasons:

- They are very well organized and professionally

…

Read More

The most obvious question here is “why do I need netlist CDC?” A lot of what you’re looking for in CDC analysis is really complex behaviors, like handshakes between different clock domains, correct gray coding in synchronizing FIFOs, eliminating quasi-static signals and the like. Deeply functional, system-level intent stuff.… Read More

As software content increases in system-on-chip and system-in-package designs, emulation has become a critical enabling technology for the software team. This technology offers software developers the opportunity to verify their code in against a high-fidelity model of the target system that actually executes fast enough… Read More

There was a “research reviewed” panel on Thursday at DAC entitled Shortening the Wires Between High-Level Synthesis and Logic Synthesis. Chaired by Alric Althoff of Tortuga Logic, the panel explored methods to deal with wire delays in high-level synthesis and logic synthesis. The four speakers and their focus were:

…

Read More

Artificial Intelligence (AI) and Machine Learning (ML) are becoming more and more commonplace in our world. We have Siri, Alexa and Google Assistant that understand our voice commands. Vision systems that recognize objects are used for facial recognition, autonomous driving, medical, geographical and many other applications.… Read More

Back in my Atrenta days (before mid-2015), we were already running into a lot of very large SoC-level designs – a billion gates or more. At those sizes, full-chip verification of any kind becomes extremely challenging. Memory demand and run-times explode, and verification costs explode also since these runs require access to … Read More

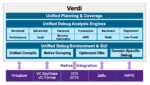

Want fast debug? Synopsys recently hosted a Webinar to show off the latest and greatest improvements to Verdi® in performance, memory demand and multi-tasking, among other areas.

Performance improvements

Taruna Reddy (PMM) and Allen Hsieh (Staff apps) presented features of the latest version, released in March – Taruna started… Read More