In today’s rapidly evolving semiconductor industry, the demand for high-quality and reliable semiconductors at a reasonable cost is increasing. This is why world-class yield management has become more and more important for fabless semiconductor companies and IDMs.

Electronic Design Automation

Accellera Update at DVCon 2023

I have a new-found respect for Lu Dai. He is a senior director of engineering at Qualcomm, with valuable insight into the ground realities of verification in a big semiconductor company. He is on the board of directors at RISC-V International and is chairman of the board of directors at Accellera, both giving him a top-down view of… Read More

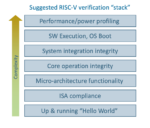

Scaling the RISC-V Verification Stack

The RISC-V open ISA premise was clearly a good bet. It’s taking off everywhere, however verification is still a challenge. As an alternative to Arm, the architecture and functionality from multiple IP providers looks very competitive, but how do RISC-V providers and users ensure the same level of confidence we have in Arm? Arm … Read More

Cadence Hosts ESD Alliance Seminar on New Export Regulations Affecting EDA and SIP March 28

Anyone interested in learning about general trade compliance concepts or how export control and sanction regulations affect the electronic systems design ecosystem will want to attend the upcoming ESD Alliance export seminar. It will be hosted by Ada Loo, chair of the ESD Alliance Export Committee and Cadence’s Group Director… Read More

Multi-Die Systems Key to Next Wave of Systems Innovations

These days, the term chiplets is referenced everywhere you look, in anything you read and in whatever you hear. Rightly so because the chiplets or die integration wave is taking off. Generally speaking, the tipping point that kicked off the move happened around the 16nm process technology when large monolithic SoCs started facing… Read More

Calibre IC Manufacturing papers at SPIE 2023

The Siemens Calibre group was very busy last week at SPIE. Calling Calibre industry leading really is an understatement. Calibre is one of the reasons Moore’s Law has continued to this day. This tool is legendary. You can get more information on the Calibre landing page including product information, resource guide, blogs

Defacto’s SoC Compiler 10.0 is Making the SoC Building Process So Easy

We have been working with Defacto since 2016 and it has been quite a journey. Putting an entire system on a chip is a driving force in the semiconductor industry. With the complexity of designing a modern SoC constantly increasing, new tools and methodologies are required and it all starts with RTL.

Defacto Technologies is an innovative… Read More

HFSS Leads the Way with Exponential Innovation

As engineers continue to design more complex systems with increasing frequency, the need for speed and capacity to solve these structures also increases. Over the years, HFSS has come a very long way and can now solve exponentially large structures with millions of unknowns. Ansys HFSS never stopped advancing, continuing … Read More

DesignCon 2023 Panel Photonics future: the vision, the challenge, and the path to infinity & beyond!

The explosion in volume and consumption of data, fueled by industry trends in virtualization, networking, and computing among others, continues to push photonic solutions forward into leading positions. On Feb 2nd, I attended a panel by Ansys at DesignCon that brought together industry experts from Intel, GlobalFoundries,… Read More

Keysight Expands EDA Software Portfolio with Cliosoft Acquisition

During the day I do M&A work inside the semiconductor ecosystem and I have been part of more than a dozen acquisitions during my career so I know a good one when I see it and I see a great one with Keysight and Cliosoft, absolutely.

Cliosoft came to SemiWiki 12 years ago when we first went online so I know them quite well. With more than… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center