S2C has been shipping FPGA prototyping platforms for SoC verification for almost two decades, and many of its customers are developing SoCs and silicon IP for Bluetooth applications. Prototyping Bluetooth designs before silicon has yielded improved design efficiencies through more comprehensive system validation, and… Read More

Electronic Design Automation

An Automated Method to Ensure Designs Are Failure-Proof in the Field

I don’t know about you, but when I think of mission-critical applications, I immediately think of space exploration or military operations. But in today’s world, mission-critical applications are all around us. Think about the cloud and how data is managed, analyzed, and shared to execute any number of tasks that have safety … Read More

WEBINAR: Revolutionizing Chip Design with 2.5D/3D-IC Design Technology

In the 3D-IC (Three-dimensional integrated circuit) chip design method, chiplets or wafers are stacked vertically on top of each other and are connected using Through Silicon Vias (TSVs) or hybrid bonding.

The 2.5D-IC design method places multiple chiplets alongside each other on a silicon interposer. Microbumps and interconnect… Read More

CEO Interview: Dr. Sean Wei of Easy-Logic

Dr. Wei has served as CEO & CTO of Easy-Logic since 2020. Prior to this role, Dr. Wei served as CTO since 2014 where he constructed the core algorithm and the tool structure of EasyECO. As the CEO, Dr. Wei focuses on building a strong company infrastructure. In his CTO role he interfaces with strategic ASIC design customers … Read More

Getting the most out of a shift-left IC physical verification flow with the Calibre nmPlatform

Who first came up with this term shift-left ? I’d assumed Siemens EDA as they use it so widely. But their latest white paper on the productivity improvements possible with shift-left Calibre IC verification flows puts the record straight: a software engineer called Larry Smith bagged the naming rights in a 2001 paper (leapfrogging… Read More

Automotive IP Certification

The electrification of cars and the growth of EVs means that more semiconductor content is being added with every new vehicle model from suppliers around the globe. There are unique concerns for automotive IP in terms of reliability, security and safety over the lifetime of the vehicle. I had the pleasure to speak with Pawini Mahajan… Read More

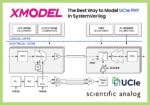

WEBINAR: UCIe PHY Modeling and Simulation with XMODEL

Join this webinar and see UCIe in action! This webinar presents the SystemVerilog models of a Universal Chiplet Interconnect Express (UCIe) interface, including both the analog circuits in the electrical layer and digital FSMs in the logical layer. The whole physical layer (PHY) model can be efficiently simulated in SystemVerilog,… Read More

Deep Learning for Fault Localization. Innovation in Verification

A new look at fault localization and repair in debug using learning based on deep semantic features. Paul Cunningham (Senior VP/GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and now Silvaco CTO) and I continue our series on research ideas. As always, feedback welcome.

The

… Read MoreWhy Secure Ethernet Connections?

While web browsing I constantly glance for the padlock symbol to indicate that the site is encrypting any of my form data by using the https prefix, which means that an SSL (Secure Sockets Layer) certificate is being used by the web hosting company. I have peace of mind knowing that my credit card information cannot be easily stolen… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry