You are probably familiar with the acronym PPA, which stands for Power/Performance/Area. Sometimes it is PPAC, where C is for cost, since there is more to cost than just area. For example, did you know that adding an additional metal layer to a chip dramatically increases the cost, sometimes by millions of dollars? It requires a … Read More

Electronic Design Automation

Synopsys – TSMC Collaboration Unleashes Innovation for TSMC OIP Ecosystem

As the focal point of the TSMC OIP ecosystem, TSMC has been driving important initiatives over the last few years to bring multi-die systems to the mainstream. As the world is moving quickly toward Generative AI technology and AI-based systems, multi-die and chiplet-based implementations are becoming essential. TSMC recently… Read More

The Quest for Bugs: “Verification is a Data Problem!”

Verification Data Analytics

Hardware Verification is a highly data-intensive or data-heavy problem. Verification Engineers recognise this and spend much of their time dealing with large and complex datasets arising from verification processes.

In “The Dilemmas of Hardware Verification” we explored the key challenges … Read More

Transformers Transforming the Field of Computer Vision

Over the last few years, transformers have been fundamentally changing the nature of deep learning models, revolutionizing the field of artificial intelligence. Transformers introduce an attention mechanism that allows models to weigh the importance of different elements in an input sequence. Unlike traditional deep learning… Read More

Lowering the DFT Cost for Large SoCs with a Novel Test Point Exploration & Implementation Methodology

With the increasing on-chip integration capabilities, large scale electronic systems can be integrated into a single System-on-Chip or SoC. New manufacturing test challenges are raised for more advanced technology nodes where both quality and cost during testing are affected. A typical parameter is test coverage which impacts… Read More

AI for the design of Custom, Analog Mixed-Signal ICs

Custom and Analog-Mixed Signal (AMS) IC design are used when the highest performance is required, and using digital standard cells just won’t meet the requirements. Manually sizing schematics, doing IC layout, extracting parasitics, then measuring the performance only to go back and continue iterating is a long, tedious… Read More

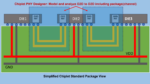

Keysight EDA 2024 Delivers Shift Left for Chiplet and PDK Workflows

Much of the recent Keysight EDA 2024 announcement focuses on high-speed digital (HSD) and RF EDA features for Advanced Design System (ADS) and SystemVue users, including RF System Explorer, DPD Explorer (for digital pre-distortion), and design elements for 5G NTN, DVB-S2X, and satcom phased array applications. Two important… Read More

Assertion Synthesis Through LLM. Innovation in Verification

Assertion based verification is a very productive way to catch bugs, however assertions are hard enough to write that assertion-based coverage is not as extensive as it could be. Is there a way to simplify developing assertions to aid in increasing that coverage? Paul Cunningham (Senior VP/GM, Verification at Cadence), Raúl … Read More

Version Control, Data and Tool Integration, Collaboration

As a follow up from my #60DAC visit with Simon Rance of Keysight I was invited to their recent webinar, Unveiling the Secrets to Proper Version Control, Seamless Data and Tool Integration, and Effective Collaboration. Karim Khalfan, Director of Solutions Engineering, Data & IP Management was the webinar presenter.

Modern… Read More

WEBINAR: Emulation and Prototyping in the age of AI

Artificial Intelligence is now the primary driver of leading edge semiconductor technology and that means performance is at a premium and time to market will be measured in billions of dollars of revenue. Emulation and Prototyping have never been more important and we are seeing some amazing technology breakthroughs including… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry