Synopsys has just announced that it has expanded its ARC processor portfolio to include a family of RISC-V processors. These will be branded under the ARC name as ARC-V and are expected to become available in 2024. This is a significant announcement which I attempt to unpack briefly below.

Electronic Design Automation

A Fast Path to Better ARC PPA through Fusion Quickstart Implementation Kits and DSO.AI

Synopsys recently presented a webinar on using their own software to optimize one of their own IPs (an ARC HS68 processor) for both performance and power through what looks like a straightforward flow from initial configuration through first level optimization to more comprehensive AI-driven PPA optimization. Also of note … Read More

Make Your RISC-V Product a Fruitful Endeavor

Consider RISC-V ISA as a new ‘unforbidden fruit’. Unlike other fruits (ISAs) that grow in proprietary orchards, RISC-V is available to all, i.e. open-source. Much like a delicious fruit can be transformed into a wide array of delectable desserts, so can RISC-V be utilized to create a plethora of effective applications across … Read More

Webinar: Fast and Accurate High-Sigma Analysis with Worst-Case Points

IC designers are tasked with meeting specifications like robustness in SRAM bit cells where the probability of a violation are lower than 1 part-per-billion (1 ppb). Another example of robustness is a Flip-Flop register that must have a probability of specification violation lower than 1 part-per-million (1 ppm). Using Monte… Read More

Generative AI for Silicon Design – Article 2 (Debug My Waveform)

Generative AI has been making waves across various industries, and its potential continues to expand. Among its many applications, one particularly intriguing area is the capacity of GenAI to explain digital design waveforms and act as a co-pilot for hardware engineers in the debugging process. In this article, we will explore

S2C’s FPGA Prototyping Accelerates the Iteration of XiangShan RISC-V Processor

S2C announced that the Beijing Institute of Open Source Chip (BOSC) adopted its Prodigy S7-19P Logic System, a VU19P-based FPGA prototyping solution, in the development of the “XiangShan” RISC-V processor. S7-19P not only accelerates the iterations of processor development but also simplifies other companies to realize … Read More

Developing Effective Mixed Signal Models. Innovation in Verification

Mixed-signal modeling is becoming more important as interaction between digital and analog circuitry become more closely intertwined. This level of modeling depends critically on sufficiently accurate yet fast behavioral models for analog components. Paul Cunningham (Senior VP/GM, Verification at Cadence), Raúl Camposano… Read More

Keynote Speakers Announced for IDEAS 2023 Digital Forum

As we all know, hearing directly from the people who actually use EDA tools, people who are solving real world problems with the latest technologies are the best source of information. Thus EDA User group meetings are always first on my event list every year which brings us to Ansys Ideas.

Ansys User Group Meeting Features Technical

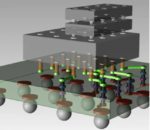

… Read MoreEnsuring 3D IC Semiconductor Reliability: Challenges and Solutions for Successful Integration

One of the most promising advancements in the semiconductor field is the development of 3D Integrated Circuits (3D ICs). 3D ICs enable companies to partition semiconductor designs and seamlessly integrate silicon Intellectual Property (IP) at the most suitable process nodes and processes. This strategic partitioning yields… Read More

Generative AI for Silicon Design – Article 1 (Code My FSM)

In today’s fast-paced world, innovation in semiconductor design is a constant demand. The need for quicker, more accurate, and innovative solutions has paved the way for exploring the potential of Generative AI (#GenerativeAI) in the realm of semiconductor design development. Can it be done? Hell yeah! In this article… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry