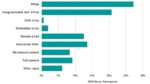

Earlier I blogged about IC and ASIC functional verification, so today it’s time to round that out with the state of FPGA functional verification. The Wilson Research Group has been compiling an FPGA report every two years since 2018, so this marks the third time they’ve focused on this design segment. At $5.8 billion… Read More

Electronic Design Automation

Interconnect Choices for 2.5D and 3D IC Designs

A quick Google search for “2.5D 3D IC” returns 669,000 results, so it’s a popular topic for the semiconductor industry, and there are plenty of decisions to make, like whether to use an organic substrate or silicon interposer for interconnect of heterogenous semiconductor die. Design teams using 2.5D and … Read More

PCIe 6.0: Challenges of Achieving 64GT/s with PAM4 in Lossy, HVM Channels

As the premier high-speed communications and system design conference, DesignCon 2023 offered deep insights from various experts on a number of technical topics. In the area of high-speed communications, PCIe has a played a crucial role over the years in supporting increasingly higher communications speed with every new revision.… Read More

Optimization Tradeoffs in Power and Latency for PCIe/CXL in Datacenters

PCI Express Power Bottleneck

Madhumita Sanyal, Sr. Technical Product Manager, and Gary Ruggles, Sr. Product Manager, discussed the tradeoffs between power and latency in PCIe/CXL data centers during a live SemiWiki webinar on January 26, 2023. The demands on PCIe continue to grow with the integration of multiple components… Read More

Big plans for state-of-the-art RF and microwave EDA

RF and microwave design is no longer confined to a few defense and aerospace EEs huddled in dark cubicles working with spreadsheets and primitive circuit simulators. Now, areas like 5G and automotive demand complex RF systems. Advanced RF and microwave EDA tools are taking on electromagnetic (EM), thermal, and power simulation,… Read More

Dr. Anirudh Devgan Elected to The National Academy of Engineering (NAE)

Having known many of the top EDA CEOs during my semiconductor tenure the common traits I have found are brilliance, humility, endurance, and a sharp sense of humor. EDA solves so many problems, complex problem after complex problem, that it takes teams of incredibly smart people to solve them. Even more difficult is leading these… Read More

The State of IC and ASIC Functional Verification

Way back in 2002 there was a study from Collett International Research on functional verification, and since 2010 the Wilson Research Group has continued that same kind of study with a new report every two years. What attracts me to this report is that it doesn’t just look at the installed base of one EDA vendor, instead it looks… Read More

Synopsys Design Space Optimization Hits a Milestone

I talked recently with Stelios Diamantidis (Distinguished Architect, Head of Strategy, Autonomous Design Solutions) about Synopsys’ announcement on the 100th customer tapeout using their DSO.ai solution. My concern on AI-related articles is in avoiding the hype that surrounds AI in general, and conversely the skepticism… Read More

Cliosoft’s Smart Storage Strategy for Better Workspace Management

Over the years storage has gotten very cheap, or has it? As a typical consumer, we take data storage for granted because access to it has gotten very cheap. Long gone are the days of being limited to 1.44MB floppy disks to store data. The smart devices we carry around with us can store 100’s of GB of data. That is a lot of data. But what about… Read More

ASIL B Certification on an Industry-Class Root of Trust IP

I have always been curious about how Austemper-based safety methodologies (from Siemens EDA) compares with conventional safety flows. Siemens EDA together with Rambus recently released a white paper on getting a root of trust IP to ASIL B certification. This provides a revealing insight beyond the basics of fault simulation… Read More

Intel’s Pearl Harbor Moment