You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4466

[filter] => raw

[cat_ID] => 157

[category_count] => 4466

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

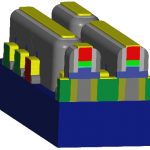

FPGA-based prototyping brings SoC designers the possibility of a high-fidelity model running at near real-world speeds – at least until the RTL design gets too big, when partitioning creeps into the process and starts affecting the hoped-for results.

The average ASIC or ASSP today is on the order of 8 to 10M gates, and that includes… Read More

There’s a nice article on timing closure by Dr. Jason Xing, Vice President of Engineering at ICScape Inc. on the Chip Design website. Not familiar with ICScape? Paul McLellan called ICScape the The Biggest EDA Company You’ve Never Heard Ofand Daniel Payne did Schematic, IC Layout, Clock and Timing Closure from ICScape at… Read More

In past years the Kaufman award, the most prestigious in EDA, has been announced around September and presented during a dinner in October or November in Silicon Valley. EDAC and CEDA, the sponsors of the award, have just announced that this time the award dinner will take place in Austin at the 50th DAC following the early Sunday … Read More

My new iPad lasts about 10 hours on a single charge and the A5X processor is designed with a 45nm process from Samsung. Processor chips for tablets like this use a multi-voltage IC design flow to reduce total power by:… Read More

At advanced process nodes, variation and its effects on the design become a huge challenge. Join Cadence® Virtuoso® experts for a series of technical webinars on variation-aware design. Learn how to use advanced technologies and tools to analyze and understand the affects of variation. We’ll introduce you to the latest Virtuoso… Read More

Silicon Creations will be presenting a paper with Berkeley Design Automation at the TSMC Open Innovation Platform (OIP) Ecosystem Forum next week where TSMC’s design ecosystem member companies and customers share real-case solutions for design challenges within TSMC’s design ecosystem:

This presentation will describe … Read More

Altera have been making use of Synopsys’s virtual platform technology to accelerate the time to volume by letting software development proceed in parallel with semiconductor development so that the software development does not need to wait until availability of hardware.

In the past, creating the virtual platform … Read More

Qualcomm VP of Engineering, Charlie Matar, will be keynoting the Apache/ANSYS seminar in Santa Clara next Thursday. Charlie is a great guy and a great speaker so you won’t want to miss this and it’s FREE! I spoke to Charlie, he will be speaking on:

Today’s complex SOC design is driven by the constant demand for high performance… Read More

ICCAD: 30 yearsby Paul McLellan on 10-09-2012 at 9:00 pmCategories: EDA, Events

ICCAD is November 5th to 8th in the Hilton San Jose (downtown).

It is very off topic, but if you are British then November 5th is the rough equivalent of July 4th when there are fireworks displays all over the country. Britain is one of very few countries that transitioned from some sort of autocracy to a democracy without having a revolution.… Read More

As SoC design has transformed from being about writing RTL and more towards IP assembly, the issue of IP quality has become increasingly important. In 2011 TSMC and Atrenta launched the soft IP qualification program. Since then, 13 partners have joined the program.

IP quality is multi-faceted but at the most basic level, an IP block… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior