At this year’s DAC, I spoke with several friends at Cadence. I got the distinct impression that something at Cadence had changed. There was a sense of pride and accomplishment that it seems to me had drifted away over the years. Now employees were speaking with true conviction about the accomplishments of the product development… Read More

Electronic Design Automation

A Big Thank You to EDA and IP

Electronic Design Automation Software and Semiconductor Intellectual Property are not so much the tail that wags the dog, rather they are like the heart of an elephant, tiny in comparison but without which there is no elephant. There is no doubt that EDA and IP have been key enablers of the semiconductor industry for the past 50 years… Read More

Synopsys: Getting To Know EDA’s Heavyweight Champion

From chip IP vendor ARM Holdings to semiconductor foundry Taiwan Semiconductor, there have been many winners from the mobile device revolution that was sparked by Apple’s introduction of the iPhone. However, while these big-ticket names get all the fame and glory, the electronic design automation space (“EDA” for short) is … Read More

High resolution Analog CMOS IC Design

My background includes transistor-level IC design, so I take delight in talking with engineers like Dr. Lanny Lewyn that are still practicing the art and science of analog IC design. Dr. Lewynis a Life Senior Member of the IEEE and has a consulting business. If you live in Santa Clara, then consider attending a live seminar on October… Read More

Computer History Museum Party!

More details are now available for the EDA 50[SUP]th[/SUP] anniversary event on October 16[SUP]th[/SUP]. If you have not been to the museum lately this is a must see event as it is all new. Definitely check out the auction items! Just do not bid against me or it will get very expensive for one of us. I’m watching Storage Wars reruns so… Read More

Cadence Grows VIP Business – What’s New?

VIPs (Verification IPs) are really important in this complex world of SoCs which involve various IPs, interfaces and continuously evolving protocols and standards, thus making the task of verifying an overall system extremely challenging. And the verification must be done in minimum possible run-time and memory consumption.… Read More

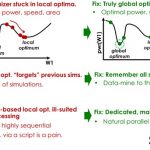

High-Sigma Standard Cell Optimization!

Standard cell optimization is an important problem, because the speed, power, and area of cells has a direct impact speed, power, and area of the whole chip. Typically, standard cell optimization been done with simple in-house local-optimizer scripts. However, these optimizers have had several flaws: they don’t properly capture… Read More

A Mixed-Signal IC Summit in San Jose

Analog and mixed-signal ICs are tougher to design and verify compared to digital, so if you want to learn more about best practices from actual AMS engineers then consider attending a summitthat is sponsored by Cadence Design Systems next Thursday, October 10th in San Jose from 8:00AM until 6:30PM.

They’ve lined up an interesting… Read More

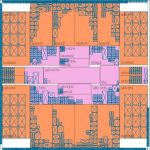

Floorplanning Merged With Synthesis

One area of iteration that is becoming more problematic is between floorplanning and synthesis. So much of timing is driven by placement that fixing timing and even power often involves not just re-synthesis and re-placement but alterations to the floorplan. The Achilles heel of existing methods is that floorplanning tools … Read More

TSMC Awards Berkeley Design Automation

One of the highlights of the TSMC 2013 Open Innovation Platform® Forum was the Partner Award Ceremony. TSMC awarded Berkeley Design Automation (BDA) with the TSMC Open Innovation Platform’s Partner of the Year Award 2013 for joint development of 16nm FinFET design infrastructure. I talked with Ravi Subramanian, BDA CEO,… Read More

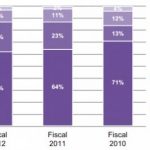

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!