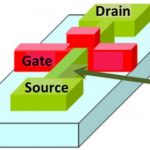

On Friday (April 19[SUP]th[/SUP]) I will be keynoting FinFET day at the EDPS conference in Monterey. This is an excellent opportunity to ask the experts about the challenges of FinFET design and manufacturing in an intimate setting (60 people). If you are interested register today and use the promo codeSemiWiki-EDPS-JFR and … Read More

Electronic Design Automation

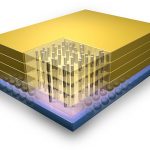

3D IC: Are We There Yet?

For the last few years, thru silicon via (TSV) based ICs have been looming in the mist of the future. Just how far ahead are they? Xiliinx famously has a high-end gate-array in production on a 2.5D interposer, Micron has a memory cube, TSMC has done various things in 3D that it calls CoWoS (chip on wafer on substrate), Qualcomm have been… Read More

TSMC Responds to Samsung!

This was the 19[SUP]th[/SUP] annual TSMC Symposium and by far the best I have attended. Finally tired of the misinformation that plagues our industry, TSMC set the record straight with wafer and silicon correlated data. TSMC shipped more than 88 MILLION logic wafers in 2012, more than any other semiconductor company, that gives… Read More

Berkeley Design Automation and the Cadence Legal Action!

SemiWiki broke the story yesterday about the Cadence legal action against Berkeley Design Automation and today I spent time with customers of both companies in Silicon Valley getting reactions. That is the advantage of working in Silicon Valley for almost 30 years, if you don’t know the right people, you certainly know the people… Read More

Mentor U2U, Not Your Father’s User Conference

I talked to Michael Buehler-Garcia about the changes Mentor is making to U2U, their user conference. It is in San Jose on April 25th at the DoubleTree.

Firstly, there are 3 great keynotes, two of whom I’ve seen speak before and can unreservedly recommend. Unfortunately I’m traveling that week and won’t be able… Read More

Cadence Sues Berkeley Design Automation

Cadence has brought a suit against Berkeley Design Automation for, as far as I can see, integrating their AFS circuit simulator with the Virtuoso Analog Design Environment (ADE) without using the (licensed) Oasis product. Since BDA is (actually was) a member of the Cadence Connections program, they have to abide by the contract… Read More

Manage your IC’s Stress for right performance

As we have moved towards lower process nodes to improve performance of ICs with higher density and functionality, many manufacturing effects have appeared which can render ICs useless, even though the layout design could be correct as per traditional design rules. What is more worrisome is the variability of these effects which… Read More

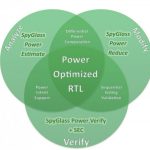

RTL Power Optimization

More so than most aspects of design, power reduction suffers from a paradox that early in the design cycle when the gains are the largest, the accuracy of power estimation is the lowest, and then late in the design cycle, when everything is known pretty much exactly it is too late to make anything other than trivial optimizations. … Read More

SoC Power Integrity Challenges

At DAC in 2012 I visited a few dozen EDA companies and blogged 32 articles, however I didn’t get to see what Apache Design (now a subsidiary of ANSYS) had to say. I did have 20 minutes today to watch their latest video on SoC Power Integrity Challenges and decided to share what I learned. If you want to watch the video at Tech Online,… Read More

Cutting the Key to 14nm Lithography

It appears that immersion lithography is now the plan of record for manufacturing ICs at 14nm. How is it possible to use 193nm wavelength light at 14nm? How can we provide the process window to pattern the such tight pitches? The secret lies in computational lithography. For 20nm, the two key innovations in computational lithography… Read More

Flynn Was Right: How a 2003 Warning Foretold Today’s Architectural Pivot