A growing trend in system design is the use of multiple ICs mounted in advanced packages, especially in high-performance computing and AI. These modern packages now integrate multiple ICs, often with high-bandwidth memory (HBM), resulting in hundreds of thousands of connections that need proper verification. Traditional… Read More

Electronic Design Automation

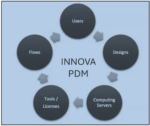

Webinar: Achieve Full Flow and Resource Management Visibility to Optimize Cost and Sustainability with Innova

The lifecycle for complex chip design includes many factors. Traditional systems focus on design tasks, associated schedules and manufacturing logistics. While these are important aspects of the project there is a lot more that can be measured, predicted and tracked. Taking a more holistic view of the project opens new opportunities… Read More

Crosstalk, 2kAmp power delivery, PAM4, and LPDDR5 analysis at DesignCon

High-speed digital (HSD) designers have long tested the limits of realizable speed. GHz frequencies are now the norm, and multi-level signaling is pushing rates higher while the long-awaited transition to optical signaling and even higher rates looms ever closer. Power density is also climbing, and data-hungry applications… Read More

2025 Outlook with Samia Rashid of Infinisim

Tell us a little bit about yourself and your company.

I am Samia Rashid, co-founder and president of Infinisim. My background is quite diverse, spanning product management, manufacturing, sales, and mergers and acquisitions. Before founding Infinisim, I was with iManage, Inc., where I played a pivotal role in growing the company… Read More

A Deep Dive into SoC Performance Analysis: Optimizing SoC Design Performance Via Hardware-Assisted Verification Platforms

Part 2 of 2 – Performance Validation Across Hardware Blocks and Firmware in SoC Designs

Part 2 explores the performance validation process across hardware blocks and firmware in System-on-Chip (SoC) designs, emphasizing the critical role of Hardware-Assisted Verification (HAV) platforms. It outlines the validation workflow… Read More

2025 Outlook with Dr. Chouki Aktouf of Defacto

Chouki Aktouf is Founder & CEO of Defacto Technologies and Co-Founder of Innova Advanced Technologies. Prior to founding Defacto in 2003, Dr. Aktouf was an associate professor of Computer Science at the University of Grenoble – France and leader of a dependability research group. He holds a PhD in Electric Engineering from… Read More

Synopsys Brings Embedded Memory to the Future with its Flexible, IP-Based Compilers

There is a revolution happening that is fueled by innovation in areas such as AI, IoT and autonomous driving. These new systems put incredible stress on next-generation semiconductor technology. Faster processing, higher density and lower latency must all be delivered with reduced power and thermal profiles. One technology… Read More

Podcast EP270: A tour of the Q3 2024 Semi Electronic Design Market Data Report with Wally Rhines

Dan is joined by Dr. Walden Rhines. Wally is a lot of things, CEO of Cornami, board member, advisor to many and friend to all. Today he is the Executive Sponsor of the SEMI Electronic Design Market Data report.

Dan explores the recently published report with Wally. Overall growth was 8.8%, a strong number but not as large as prior quarters.… Read More

Accelerating FPGA-Based SoC Prototyping

FPGA-based prototyping offers advantages such as high-speed operation, real-world environment testing, and parallel execution that cannot be matched by software simulations alone. It enables developers to validate their designs and initiate software development long before the final silicon is ready. At the same time,… Read More

Chiplet integration solutions from Keysight at Chiplet Summit

Chiplets continue gaining momentum, fueled in large part by applications for AI and 5G/6G RFICs. Keysight has a strong presence at this year’s Chiplet Summit in Santa Clara, which includes Simon Rance in a super panel discussing “Chiplets: The Key to Solving the AI Energy Gap” and Nilesh Kamdar with a keynote… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center