You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4178

[filter] => raw

[cat_ID] => 157

[category_count] => 4178

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

I first heard about Andrew Yang back in 1993 when he founded a Fast SPICE company called Anagram, then acquired by Avant! in 1996. Andrew’s latest EDA company Apache Design, Inc.was started in 2001, then acquired by ANSYS in 2011. Most EDA mergers simply don’t work because of one or more reasons, like:

…

Read More

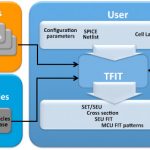

There are two ways to see how resistant your designs are to single-event errors (SEE). One is to take the chip or even the entire system and put it in a neutron beam and measure how many problems occur in this extreme environment. While that may be a necessary part of qualification in some very high reliability situations, it is also … Read More

Gary Smith has been talking about how the electronic system level (ESL) is where the future of EDA lies as design teams move up to higher levels encompassing IP blocks, high level synthesis, software development using virtual platforms and so on. At DAC this year in Austin he talked about how the fact that EDA controls the modeling… Read More

My Samsung Galaxy Note II lasts about two days on a single battery charge, which is quite the improvement from the Galaxy Note I with only a one day battery charge. Mobile SoCs are being constrained by battery life limitations, and consumers love longer-laster devices.

There are at least two approaches to Design For Power:

…

Read More

I could have written the sequence of the title in reverse order, but no, design is the one which initiates the need of a particular flow and the flow needs support of EDA tools to satisfy that need. It’s okay if the design is small; some manual procedures and workarounds/scripts may be able to perform certain jobs. However, as the design… Read More

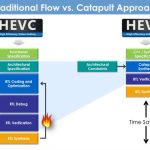

Of course if you are in the business of selling high-level synthesis (HLS) tools then the obvious answer is immediately. Start at 9am tomorrow morning. But a more realistic answer is when you are having to do something completely new. If you are working on a legacy design, perhaps with pre-existing IP, then moving the design up to … Read More

Well, Sweden is not noted for its carnivals, Brazil is not noted for it’s tall blonde blue-eyed women, Sweden’s climate is not great for growing sugar cane and Brazil’s isn’t great for reindeer. Both countries speak languages with odd-sounding vowels but they are not the same language. But, ding, Jasper… Read More

Sometimes press releases just make me scratch my head. Today’s example comes from IBM: after tying PowerPC and Power.org in knots for almost 20 years with rules and restrictive licensing, IBM breaks ranks and sets up ANOTHER consortium with different players.… Read More

GenApSys is a biotech company developing proprietary DNA sequencing technology. As part of that they develop their own custom sequencing chips. These have an analog component and like many people they use the Cadence Virtuoso analog design environment for this.

I talked to Hamid Rategh who is GenApSys’s VP engineering.… Read More

Founders

The founder, Ghislain Kaiser, spent about 10 years at STMicroelectronics, mainly in multimedia groups and for the wireless market. At this time, he was a power expert and tasked with making the chips use less power. The first thing he did was to look at what tools existed on the market. They wanted to use off the shelf tools… Read More

Facing the Quantum Nature of EUV Lithography