In the semiconductor ecosystem, several partners (or better to say stakeholders) join together in the overall value chain to finally output the most coveted chip, err I should say SoC these days. It becomes really interesting when we start analyzing the real value added by each of them, none appears to be less. Well, then to whom … Read More

Electronic Design Automation

What’s Behind Carbon System Exchange – How Will it Scale?

Earlier this year, when I was looking at Carbon’spast year performance which provided record breaking revenue with whopping jump in bookings, one thing was certain that Carbon Performance Analysis Kits (CPAKs) would drive major growth in future, not only for Carbon, but also for the semiconductor industry. It will initiate … Read More

IP and Design Management Done Right

At DACin San Francisco this past June I was able to visit and blog about two dozen EDA companies, however there were so many more products and events to see that I couldn’t possibly have enough time to enjoy them all. Fortunately for me there were plenty of videos made of vendor presentations, so this week I got caught up a bit by… Read More

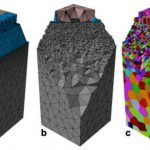

ANSYS Tools Shine at FinFET Nodes!

In the modern semiconductor ecosystem we are seeing rapid advancement in technology breaking past once perceived limits; 28nm, 20nm, 16-14nm, 10nm and we are foreseeing 7nm now. Double and multi-patterning are already being seen along with complex FinFET structures in transistors to gain the ultimate advantages in PPA from… Read More

Designing SmartCar ICs

When I upgraded cars from a 1988 to 1998 Acura it seemed like my car had become much smarter with a security chip in the key, security codes in the radio and a connector for computer diagnosis, however in today’s modern auto there’s a lot more mixed-signal design content. Micronasand Synopsysgot together and hosted … Read More

Place & Route with FinFETs and Double Patterning

Place & route in the 16/14nm era requires a new approach since it is significantly more complex. Of course, every process generation is more complex than the one before and the designs are bigger. But modern processes have new problems. The two biggest changes are FinFETs and double patterning.

FinFETs, as I assume you know,… Read More

A Complete Timing Constraints Solution – Creation to Signoff

With the unprecedented increase in semiconductor design size and complexity design teams are required to accommodate multiple design constraints such as multiple power domains for low power design, multiple modes of operation, many clocks running, and third party IPs with different SDCs. As a result timing closure has become… Read More

SiC and Si Power Devices

ICs for consumer electronics are often battery powered, which are considered low voltage designs. On the other end of the IC spectrum are high voltage devices used in many industrial applications like: automotive, aerospace, data centers, transportation and power generation. … Read More

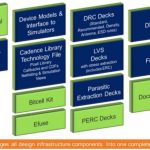

Mentor at TSMC OIP, 16nm, and 10nm

On Tuesday, September 30, TSMC hosts another Open Innovation Platform Ecosystem forum at the San Jose Convention Center. Have you registered? This year includes 30 technical sessions from TSMC’s ecosystem partners, divided into three separate tracks. I’ll be hanging out in the EDA track, listening to various takes on 16nm FinFET… Read More

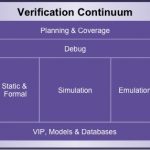

Synopsys Verification Continuum

Verification spans a number of different technologies, from virtual platforms, RTL simulation, formal techniques, emulation and FPGA prototyping. Going back a few years, most of these technologies came from separate companies and one effect of this was that moving the design from one verification environment to another required… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center