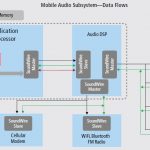

Today, Smartphones and mobile devices have become center of innovation with multiple functions getting into them. Considering the audio or voice application, there can be multi-way conferencing, video chat, complete audio/video streaming, gaming, voice triggering and recognition,… you name an application, and it will … Read More

Electronic Design Automation

HiFi Sounds Better than Ever

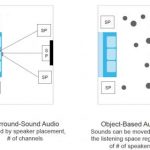

If you think that the sound atmosphere created by Dolby or Surround–sound audio is the best you can achieve today by using complexes algorithms on DSP, like I thought before knowing about “Object-Based Audio”, you must read these lines! In fact Surround-sound Audio is limited by the number of speakers installed in a room, or a car,… Read More

A Group of Happy Employees that Excels in Everything They Do!

I visited AtrentaNoida in August 2013 during the inauguration of its newly expanded facility. At that time, I had written about the beautiful environment Atrenta has, with its presence at many sites across the world in my blog – “Innovation + Thoughtful Management = Productive Expansion”. Innovation cannot happen without happy… Read More

Semiconductor Design: Chips to Systems!

This is the 20[SUP]th[/SUP] year of DesignCon and I’m really looking forward to it. While I haven’t attended all 20 I certainly have attended the majority of them. Now it is like a college reunion for me seeing all sorts of friends and former coworkers. One of them is even a keynote but more on that later. This year there are 14 conference… Read More

Curie to Bring New Dimensions in Wearables!

In the past year, seeing the kinds of wearables doing what Smartphones can do, I wasn’t much excited about wearables; however after looking at what Intelhas demonstrated in CES 2015, a button sized SoC called Curie, I get to believe that it will be a game changer in wearables and would let Intel do what it couldn’t do with Smartphone… Read More

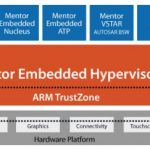

Mentor Moves to Enter IoT Fray

In December I signed up for an IoT “lunch and learn” hosted by Mentor Graphics. There were a number of surprising things about the session. The first and most obvious is that it was really a “breakfast-to-lunch and learn”. Starting at 9AM and going through the end of lunch, it was packed full of ‘learning.’ It was also packed full of … Read More

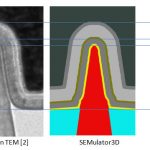

Coventor Panel at IEDM Digs into Variation Issues

Recently I attended a panel discussion on variability in semiconductor fabrication hosted by Coventor in conjunction with the IEEE IEDM conference in San Francisco. The IEEE bills the conference as “the world’s pre-eminent forum for reporting technological breakthroughs in the areas of semiconductor and electronic device… Read More

Prototyping Kits to Accelerate IP Development & Integration into SoCs

With growing SoC size, complexity, software and hardware content in it and shrinking time-to-market, the SoC design completion in time has become increasingly dependent on IP which need to be sourced (internally or externally), customized according to the design need and integrated together into the SoC. While IP providers… Read More

Facts Support New Emergence in Semiconductor Landscape

As we left an exciting year 2014 which is poised to record 7+ % increase in semiconductor revenue (~ $338 B) compared to 2013 (~ $315 B) and entered into another promising year 2015 for semiconductors, I looked back over the year bygone and collected inferences from some of the major important events which clearly convey how 2015 can… Read More

WLAN Design Optimization at Lantiq

Right now I’m typing on my MacBook Pro computer connected to the Internet through WiFi, thanks to the electronics in both my laptop and WiFi router. I kind of take WiFi for granted because it is so ubiquitous throughout my daily life, yet there are IC designers at companies like Lantiq Semiconductorthat have to design and optimize… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era