After knowing about the challenges involved in validating multicore systems and domains of system and application level tracing as explained by Don Dingee in his article “Tracing methods to multicore gladness” which is based on the first part of Mentor Embedded multicore whitepaper series, it’s time to take a deeper insight … Read More

Electronic Design Automation

Managing Semiconductor IP

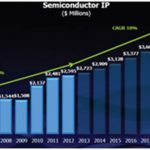

SemiWiki blogger Eric Esteve does an excellent job writing about all of the semiconductor IP available, and the popularity of IP is only growing more each year. Here’s a projection from IBS about semiconductor IP showing revenues of $4.7B by 2020:

Analyst Gary Smith divides IP into three broad categories: Functional, Foundation… Read More

Analyzing Power Nets

One of the big challenges in a modern SoC is doing an accurate analysis of the power nets. Different layers of metal have very different resistance characteristics (since they vary so much in width and height). Even vias can cause problems due to high resistance. Typically power is distributed globally on high-level metal layers,… Read More

Not All RTL Synthesis Approaches are the Same

My first experience with logic synthesis was at Silicon Compilers in the late 1980s using a tool called Genesil. Process technology since that time has moved from 3 um down to 20 nm, so there are new challenges for RTL synthesis. Today you can find logic synthesis tools being offered by the big three in EDA: Synopsys, Cadence, Mentor… Read More

Methodics Access Controls

My PhD thesis is titled The Design of a Network Filing System. Yes, that was a research topic back then (and yes, we did call them filing systems not file-systems). One big chapter was on access controls. There are several problems with designing an access control system:

- it needs to be possible to implement it efficiently

- it needs

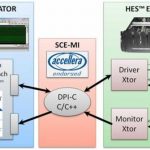

Aldec increasing the return on simulation

Debate rages about which approach is better for SoC design: simulation, or emulation. Simulation proponents point to software saving the need for expensive hardware platforms. Emulation supporters stake their claims on accuracy and the incorporation of real-time I/O. A few years back, some creative types coined the term SEmulation,… Read More

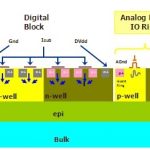

Analyze Substrate Noise in SoC Design?

Often substrate noise analysis takes place when everything is there on the chip, but that stage comes near the tape-out which is too late to make major changes in architecture, placement, introducing noise protection circuitry for the victims and so on. It was okay when there used to be very little analog content on the chip. But … Read More

Tracing methods to multicore gladness

Multiple processor cores are now a given in SoCs. Grabbing IP blocks and laying them in a multicore design may be the easy part. While verification is extremely important, it is only the start – obtaining real-world performance depends on the combination of multicore hardware and actual application software. What should engineers… Read More

Johan Peeters on quick IP check through Cdiff

On the face of it, if we consider a simple ‘diff’ utility, it doesn’t need any explanation; almost everyone in our community would have used it. But imagine the CTO of a company investing his time in explaining how beneficial a specialized ‘Cdiff’ function can be in evaluating IP. Today’s SoC design world can’t live without IP and … Read More

Verification of Wireless RFIC Designs

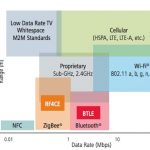

Wireless technology is all around as I use cellular on an Android phone, WiFi to connect my MacBook Pro to the internet, Bluetooth for a headset, ANT+ for my cycling computer, and NFC to speed up electronic payments on the Android phone. Here’s a big picture look at some of the modern wireless standards available to choose from:… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era