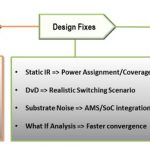

By the time that your SoC comes back from the fab and you plugin it into a socket on a board for testing, it’s a little late in the cycle to start thinking about reliability concerns like: dynamic voltage drop, noise coupling, EM (Electro-Migration), self-heating, thermal analysis and ESD (Electro-Static Discharge). They… Read More

Electronic Design Automation

GPP, GPU or Embedded Vision Dedicated Processor?

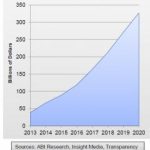

Before answering the question we should try to define what is behind “Vision”, which type of applications and evaluate this heterogeneous market weight. Embedded Vision (EV) is the use of computer vision in embedded systems to interpret meaning from image or video. In fact vision processing requires a lot of maths functions that… Read More

Advances in Nanometer Analog and Mixed Signal Design!

Mentor’s annual user group meeting at the Doubletree Hotel in San Jose, CA is coming up on Tuesday, April 21[SUP]st[/SUP]. This complementary event provides a unique opportunity to share design techniques and exchange ideas with other users and experts in the design community. As you may have read I am the star of the show; moderating… Read More

Beyond CMOS: Three Industry Teams Aim at Next Generation of High-performance Computing

Given the current limitations with CMOS designs, such as low temperature thresholds and efficiency in power consumption, there is a vast need to expand into superconducting computers in order to manage consumers’ need for power and performance. Although supercomputers require extremely low temperatures, they are capable… Read More

Safety Dominates Agenda in DAC’s Automotive Track

The connected car movement is in full bloom, making headlines in the trade media on how the cutting-edge electronics will transform the twenty-first century driving experience. However, a closer look at the Internet of cars juggernaut shows that safety and security of the networked vehicle are still a major stumbling block.… Read More

Sidense NVM Scores Qualification on GLOBALFOUNDRIES 28nm SLP and HPP

A tremendous number of chips being designed for today’s products require some sort of onboard data storage. The size of these needs range from a handful of bytes, for trim and calibration storage, to something much more substantial like boot code storage. In both of these examples the storage ideally should be nonvolatile, with… Read More

Cu-Pillar in Advanced Logic Devices

In 2001, flipchip with solder bump was already a dominant technology and it was replacing wire bonding as the main interconnection choice for a growing number of devices. It was offering fine pitch interconnections for increased I/O counts. In the solder bump process, a bump is formed on the chip and on the package substrate and … Read More

ANSYS Enters the League of 10nm Designs with TSMC

The way we are seeing technology progression these days is unprecedented. It’s just about six months ago, I had written about the intense collaboration between ANSYSand TSMCon the 16nm FinFET based design flow and TSMC certifying ANSYS tools for TSMC 16nm FF+ technology and also conferring ANSYS with “Partner of the Year” award.… Read More

Starvision Pro: Lattice Semiconductor’s Experience

During SNUG I took the opportunity to chat to Choon-Hoe Yeoh of Lattice Semiconductor about how they use Concept Engineering’s Starvision Pro product. He is the senior director of EDA tools and methodologies there.

Lattice Semiconductor is a manufacturer of low-power, small-footprint, low-cost programmable logic devices.… Read More

Archives from TI’s Baseband Glory – Part 1

In 1992, nearly two years after Britain’s Acorn Computers joined hands with Apple and VLSI to create Advanced RISC Machines or ARM, the semiconductor upstart landed its first major licensing breakthrough. In retrospect, while Apple’s Newton handheld computer had played a key role in creating the ARM venture, Texas… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era