At the recent TSMC OIP symposium, Bill Acito from Cadence and Chin-her Chien from TSMC provided an insightful presentation on their recent collaboration, to support TSMC’s Integrated FanOut (InFO) packaging solution. The chip and package implementation environments remain quite separate. The issues uncovered in bridging… Read More

Electronic Design Automation

A Connectivity Verification Idea

A Wirble

In case you hadn’t noticed, I like to write from time to time about EDA product ideas. I assume these are somewhat original, but given the maxim “there’s nothing new under the sun…”, I may well be wrong. In any event, I like to share these ideas if only to demonstrate that innovation in EDA is not stalled because we’ve run out big,… Read More

SpyGlass World at Levi Stadium, October 21st

I suppose you might have something better to do next Wednesday but, seriously, it had better be pretty good. I admit I’m biased (I was the Atrenta CTO until very recently) but even given that and mixing metaphors, Atrenta really knocked it out of the park when they got the 49er stadium for their User Group meetings. You don’t have to … Read More

Tensilica 4th generation DSP IP is a VPU

You may not know Tensilica DSP IP core, but you probably use Tensilica DSP powered systems in your day to day life. Every year, over 2 billion DSP cores equip IC in thousands of designs supporting IoT, Mobile Phones, Storage/SSD, Networking, Video, Security, Cameras… and more. Why DSP processing, the foundation of all Tensilica… Read More

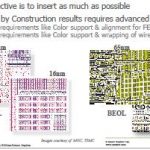

Meeting DFM Challenges with Hierarchical Fill Data Insertion

To describe the latest methodology for the addition of Design for Manufacturability fill shapes to design layout data, it’s appropriate to borrow a song title from Bob Dylan – The Times They Are A Changin’. The new technical requirements are best summarized as: “The goal is now to add as much fill as possible, which (ideally) looks… Read More

Applying EDA Concepts Outside Chip Design

(I changed the title of this piece as an experiment) Paul McLellan recently wrote on the topic of new ventures crossing the chasm (getting from initial but bounded success to a proven scalable business). That got me to thinking about the EDA market in general. In some ways it has a similar problem, stuck at $5B or so and single-digit… Read More

S2C ships UltraScale empowering SoFPGA

Most of the discussion around Xilinx UltraScale parts in FPGA-based prototyping modules has been on capacity, and that is certainly a key part of the story. Another use case is developing, one that may be even more important than simply packing a bigger design into a single part without partitioning. The real win with this technology… Read More

Five Areas at #53DAC That Require Your Contribution

The 53rd DAC (Design Automation Conference) is some 8 months away, however to make this conference and exhibit another success requires planning, people and awareness. That’s where you come in, because you can contribute your expertise in five different areas:

[LIST=1]

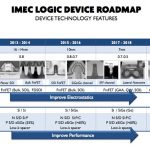

IMEC and Cadence Disclose 5nm Test Chip

Recently imec and Cadence disclosed that they had fabricated 5nm test chips. This afternoon Dan Nenni and I had a conference call with Praveen Raghavan, principal engineer at imec, and Vassilios Gerousis, distinguished engineer at Cadence to get more details on what the test chip is and what was learned.

First off Vassilios really… Read More

Cadence Outlines Automotive Solutions at TSMC OIP Event

I used to joke that my first car could survive a nuclear war. It was a 1971 Volvo sedan (142) that was EMP proof because it had absolutely no semiconductors in the ignition system, just points, condensers and a coil. If you go back to the Model T in 1915 you will see that the “on-board electronics” were not that different. However, today’s… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center