You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4466

[filter] => raw

[cat_ID] => 157

[category_count] => 4466

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

Dan is joined by Rimpy Chugh, a Principal Product Manager at Synopsys with 14 years of varied experience in EDA and functional verification. Prior to joining Synopsys, Rimpy held field applications and verification engineering positions at Mentor Graphics, Cadence and HCL Technologies.

Dan explores the expanding role of static… Read More

Jay Vleeschhouwer, Managing Director of Software Research at Griffin Securities, is a noted financial analyst who does a yearly presentation on the State of EDA during the Design Automation Conference (DAC). This year was no exception. He and I spent a memorable afternoon discussing the Synopsys-Ansys merger and startups. … Read More

3D IC was a very popular topic at DAC. The era of heterogeneous, multi-chip design is here. There were a lot of research results and practical examples presented. What stood out for me was a panel at the end of day two of DAC that was hosted by Siemens. This panel brought together an impressive group of experts to weigh in on what was really… Read More

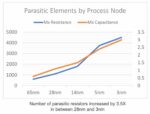

With advanced semiconductor processes continuing to shrink, the number and complexity of parasitic elements in designs grows exponentially contributing to one of the most significant bottlenecks in the design flow. Undetected parasitic-induced issues can be extremely costly, often resulting in tape-out delays.

Silvaco… Read More

Given my SpyGlass background I always keep an eye out for new ideas that might be emerging in static and formal verification. Whatever can be covered through stimulus-free analysis reduces time that needn’t be wasted in dynamic analysis, also adding certainty to coverage across that range. Still, advances don’t come easily. … Read More

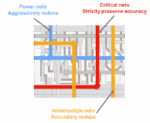

In Silvaco’s July 2025 video presentation at the 62nd Design Automation Conference (DAC), Senior Staff Applications Engineer Tim Colton introduced Jivaro, a specialized parasitic reduction tool designed to tackle the escalating challenges of post-layout simulation in advanced IC designs. As semiconductor nodes… Read More

By Hossam Sarhan

Communication has become the backbone of our modern world, driving the rapid growth of the integrated circuit (IC) industry, particularly in communication and automotive applications. These applications have increased the demand for high-performance analog and radio frequency (RF) designs.

However, designing… Read More

Shelly Henry is the CEO and Co-Founder of MooresLabAI, bringing over 25 years of semiconductor industry experience. Prior to founding MooresLabAI, Shelly led silicon teams at Microsoft and ARM, successfully delivering chips powering billions of devices worldwide. Passionate about driving efficiency and innovation, Shelly… Read More

Power densities on chips increased from 50-100 W/cm2 in 2010 to 200 W/cm2 in 2020, creating a significant challenge in removing and spreading heat to ensure reliable chip operation. The DAC 2025 panel discussion on new cooling strategies for future computing featured experts from NVIDIA Research, Cadence, ESL/EPFL, the University… Read More

Digital audio processing is evolving into an art form, particularly in high-end applications such as automotive, cinema, and home theater. Innovation is moving beyond spatial audio technologies to concepts such as environmental correction and spatial confinement. These sophisticated soundscapes are driving a sudden increase… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!