Next week is the Mentor U2U Conference in Silicon Valley. By chance I had coffee with one of the U2U keynote speakers while we were waiting for the FD-SOI Symposium to start last week and can tell you this FREE event is one you don’t want to miss:… Read More

Electronic Design Automation

Debugging is the whole point of prototyping

The prototype is obviously the end goal of FPGA-based prototyping, however success of the journey relies on how quickly defects can be found and rectified. Winning in the debug phase involves a combination of methodology, capability, and planning. Synopsys recently aired a webinar on their HAPS environment and its debug ecosystem.… Read More

Join the Multi-die IC session on April 21 at EDPS 2016 in Monterey, CA

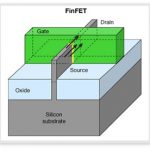

Following Moore’s Law down to 10 or even 7 nm labeled feature size demands US $ hundreds of millions of up-front investment, a very large design team and two or more years of development time. These parameters suggest that it only makes sense for very high volume applications to continue on the shrink path to increase SoCs’ functionalities.… Read More

EDAC Name Changing for ESDA, but what about IP ?

The EDA Consortium (EDAC) has changed name for Electronic Systems Design Alliance (ESD Alliance). That’s a good reminder that IC are developed (thanks to Design Automation) to be integrated into a System. A wide design ecosystem support system development, including embedded software, design intellectual property (IP), … Read More

“Thinking Outside the Chip”

While pushing Moore’s Law’s boundaries in the world of 2D packaging, companies are starting to explore nontraditional approaches towards designing integrated circuit chips. 2D packaging is currently the most used method in designing chips in the industry, and while it leads in efficiency of power and performance, it lacks … Read More

Making PLM Actually Work for for IC Design

The topic of Product Lifecycle Management (PLM) conjures up images of usage on airplanes, tanks and cars. That’s because it was developed decades ago to help make product development and delivery more efficient for big expensive manufactured products. It worked well for its intended markets by combining and managing all the … Read More

Neural Networks Poised to Make Big Changes in Our World

Probably the most interesting thing about Neural Networks is how they can be used for complex recognition tasks that we as people can easily perform but we might have a lot of trouble explaining how. One very good example of a problem that Neural Networks can tackle is determining when people are making a fake smile. Intuitively we… Read More

Custom Layout Productivity Gets a Boost

In the 1970’s, when Moore’s Law was still in its infancy, Bill Lattin from Intel published a landmark paper [1]. In it he identified the need for new design tools and methods to improve layout productivity, which he defined as the drawn and verified number of transistors per day per layout designer. He said existing … Read More

The Importance of Transistor-Level Verification

According to the IEEE Std 1012-2012, verification is the acknowledgement that a product is in satisfactory condition by meeting a set of rigorous criteria. [3] Transistor-level verification involves the use of custom libraries and design models to achieve ultimate performance, low power, or layout density. [2] Prediction… Read More

Webinar alert – Taking UVM to the FPGA bank

UVM has become a preferred environment for functional verification. Fundamentally, it is a host based software simulation. Is there a way to capture the benefits of UVM with hardware acceleration on an FPGA-based prototyping system? In an upcoming webinar, Doulos CTO John Aynsley answers this with a resounding yes.… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center