The advantage of working with cache memory is the great boost in performance you can get from working with a local high-speed copy of chunks of data from main memory. The downside is that you are messing with a copy; if another processor happens to be working in a similar area, there is a danger you can get out of sync when reading and writing… Read More

Electronic Design Automation

Lighting Up The Cloud

In our rush to imagine a world populated with IoT devices, tech advances at the top end of this ecosystem (the cloud) don’t seem to get much airtime. But this isn’t because they are limited to modest refinements. As one example, there is active technology development in connectivity around fiber-based communications within the… Read More

Tuning Analog IP for High Yield at SMIC

Analog IP is more difficult to design and optimize for a given process node compared to digital IP, so any automation for analog designers is always welcome. The engineers at SMIC in China have customers that design analog IP and often they need to know how to optimize it for a specific process, so I watched a presentation by Josh Yang,… Read More

2015 3D ASIP conference: Thar’s Gold in Them Thar Hills!

Last week I presented at the 3D ASIP EDA Tutorial and attended the Conference. In previous years, leading edge papers were presented from large companies pushing a solution to meet their needs. These companies had the resources and clout to achieve some astounding successes, but the lingering question was: “what other product… Read More

Connections to Internet Drives Semiconductors

We are going to see a big reversal in what connects to the internet in next five years. At the start of this century there were about 488 million internet connections; 85% of those were connected to people for web browsing, e-mails, on-line services etc. and only 15% were used for embedded systems, remote sensing and control, and M2M… Read More

A Synergistic Chip-Package-System Analysis Methodology

Looking back, 2015 was a significant year for mergers and acquisitions in the EDA industry. The Semiwiki team maintains a chronology of major transactions here.

As I was reviewing this compendium, one of the entries that stands out is the acquisition of Apache Design Solutions by Ansys, Inc. a couple of years ago.

At that time, there… Read More

Leveraging HLS/HLV Flow for ASIC Design Productivity

Imagine how semiconductor design sizes leapt higher with automation in digital design, which started from standard hardware languages like Verilog and VHDL; analog design automation is still catching up. However, it was not without a significant effort put in moving designers from entering schematics to writing RTL, which… Read More

HDCP 2.2, Root of Trust, Industry’s First SHA-3 Security IP from Synopsys

Did you know that by 2020 90% of cars will be connected to Internet? Great, but today, there are already more than 100 car models affected with security flaws (Source: theguardian.com, 2015). That 320 apps are installed on average smartphone device? It would be a complete success, but 43% of Android devices allow installation of… Read More

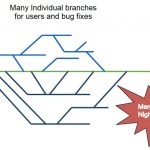

How to Overcome HW Project Release Nightmares

Is a software development release methodology a “square peg in a round hole” when it comes to hardware design? To answer this question we have to look at how exactly hardware design projects differ from their software counterparts. Intuitively we know they are fundamentally different. Let’s take a second to dig deeper to understand… Read More

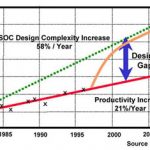

How to Solve the Business Gap in SEMI Industry?

This white paper about Cadence innovative mixed-signal IP concept “Cadence Multi-Link PHY IP (SerDes, Analog Front-end, and DDR) to Design SoC Platform breaking the “Business Gap” on 14/16FF” describe the problem, the emergence of a “business gap” linked with incredibly high development cost when targeting most advanced … Read More

Intel’s Pearl Harbor Moment