FMCAD (Formal Methods in Computer Aided Design) is a technical conference with a 20-year pedigree. This is a conference for serious formal methods teams. Key notes are from Berkeley and UCLA, committee members are all formal heavyweights and best I can tell, there is no exhibitors area.… Read More

Electronic Design Automation

Making photonic design more straightforward

The arrival of optical computing has been predicted every year for the last fifteen years. As with any other technology backed by prolific research, lofty goals get dialed back as problems are identified. What emerges first is a set of use cases where the technology fits with practical, realizable implementations.

When it comes… Read More

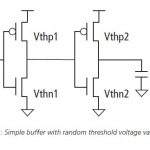

Why is Low Frequency Noise Measurement for ICs Such a Big Deal?

Even digital designers need to be aware of how noise impacts their circuits because most clocked designs today use a Phase Locked Loop (PLL) block which contains a circuit called a Voltage Controlled Oscillator (VCO) that is quite sensitive in operation to the effects of noise and process variation. As process node scaling continues… Read More

Getting out of DIY Mode for Virtual Prototypes

Virtual prototyping has, inexplicably, been largely a DIY thing so far. Tools and models have come from different sources with different approaches, and it has been up to the software development team to do the integration step and cobble together a toolchain and methodology that fits with their development effort.

That integration… Read More

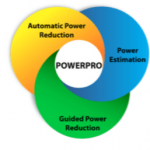

Mentor Webinar on Power Exploration for Optimizing Power

There are a lot of clever techniques to automatically find and even implement methods for register gating and memory gating, but the bulk of power-saving still depends on designer and architect insight based on expected range of use of a device, complemented by practical use-case simulations. Of course this team needs to be able… Read More

RTL Design Restructuring Explained

Modern SoC designs can use billions of transistors where transistors are grouped into gates, then gates grouped into cells, then cells grouped into blocks, blocks grouped into modules, and so on, creating a complex hierarchy. What a front-end designer conceives of logically for a hierarchy will differ from how an optimized physical… Read More

Solutions for Variation Analysis at 16nm and Beyond

Variation is still the tough nut to crack for advanced process nodes. The familiar refrain of lower operating voltages and higher performance requirements make process variation an extremely important design consideration. As far back as the early 2000’s design teams have been looking for a better approach to model variation… Read More

3 Small-Team Design Productivity Challenges Managed

“Data management tools? We use small teams doing small designs. Each project only has two or three designers. Everyone uses the same EDA tools. Why do we need another tool for collaboration?” Good question. If you enjoy frequent meetings and redoing work because someone didn’t understand the status of IP blocks, the answers may… Read More

Low Power Design – a Server Perspective (Webinar)

Most of what you have read about design for low power has probably focused on mobile devices where power consumption constraints tend to outweigh performance objectives. These devices use aggressive power switching strategies, based on the reasonable assumption that parts or all of the device can be powered down at any given … Read More

Next Book Signing: Linley Processor Conference 2016!

It is a busy month for book signings but it is a pleasure to do it for the greater good of the semiconductor industry. It really is an honor to meet the people who keep our electronic devices on the leading edge of technology, absolutely.

The Linley Processor Conference is on September 27[SUP]th[/SUP]and 28[SUP]th[/SUP] at the Hyatt… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center