I’ve lived and worked in Silicon Valley for 13 years, but since 1995 I’ve been in the Silicon Rainforest (aka Oregon) where the world’s number one semiconductor company Intel, has a large presence, along with dozens of smaller high-tech firms. In the past year I’ve started to attend events organized … Read More

Electronic Design Automation

Synchronizing Collaboration

Much though some of us might wish otherwise, distributed development teams are here to stay. Modern SoC design requires strength and depth in expertise in too many domains to effectively source from one site; competitive multi-national businesses have learned they can very effectively leverage remote sites by building centers… Read More

Calibre Can Calculate Chip Yields Correlated to Compromised SRAM Cells

It seems like I have written a lot about SRAM lately. Let’s face it SRAM is important – it often represents large percentages of the area on SOC’s. As such, SRAM yield plays a major role in determining overall chip yields. SRAM is vulnerable to defect related failures, which unlike variation effects are not Gaussian in nature. Fabrication… Read More

SPIE 2017: Irresistible Materials EUV Photoresist

Irresistible Materials (IM) is a spin-out of the University of Birmingham in the United Kingdom that has been doing research on Photoresist and Spin-On Carbon hard masks for 10 years, most recently with Nano-C on chemistry development. IM has developed a unique EUV photoresist and they are now looking for partners to help bring… Read More

Webinar: Chip-Package-System Design for ADAS

When thinking of ADAS from an embedded system perspective, it is tempting to imagine that system can be designed to some agreed margins without needing to worry too much about the details of the car environment and larger environment outside the car. But that’s no longer practical (or acceptable) for ADAS or autonomous systems.… Read More

The Rise of Transaction-Based Emulation

One serious challenge to the early promise of accelerating verification through emulation was that, while in theory the emulator could run very fast, options for driving and responding to that fast model were less than ideal. You could use in-circuit emulation (ICE), connecting the emulation to real hardware and allowing you… Read More

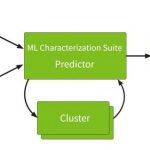

Machine Learning Accelerates Library Characterization by 50 Percent!

Standard cell, memory, and I/O library characterization is a necessary, but time-consuming, resource intensive, and error-prone process. With the added complexity of advanced and low power manufacturing processes, fast and accurate statistical and non-statistical characterization is challenging, creating the need … Read More

When Will we Replace the 3.5 mm Jack in Modern Phones?

You have certainly experienced that modern mobile phones are used for more than phone calls and do not have room for multiple connectors. A new approach for audio connectivity is needed, allowing product designers to retire the 3.5mm jack. Considering the USB audio protocol to replace the analog audio solutions, typically using… Read More

CEO Interview: Sanjay Keswani of Consensia

Sanjay Keswani founded Consensia in 2013. He has deep experience in the high-tech industry, guiding some of the world’s high profile technology brands through complex innovation and business transformation projects including companies such as Atmel, KLA-Tencor, Hughes Aircraft, and Motorola Mobility. Consensia customers… Read More

Everything a Designer Wants to Ask About FDSOI

So you’ve got questions about FD-SOI? For chip designers in Silicon Valley, there’s a great opportunity to get answers from some of the world’s leading design experts. It’s coming up fast: April 14th, the SOI Consortium is organizing a full day of FDSOI tutorials for chip designers. Bear in mind that … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center