Breker Verification Systems solves challenges across the functional verification process for large, complex semiconductors. This includes streamlining UVM-based testbenches for IP verification, synchronizing software and hardware tests for large system-on-chips (SoCs), and simplifying test sets for hardware emulation… Read More

Electronic Design Automation

Silvaco on Simulation of Reliability and NBTI Aging in MOS Microelectronics

Silvaco was founded the same year I entered the EDA industry (1984) fresh from University. I first met them at the Design Automation Conference in Albuquerque, New Mexico, and have been an active observer of their growth ever since. In fact, Silvaco is now the largest privately held EDA company and is growing at a rapid pace. In 2014… Read More

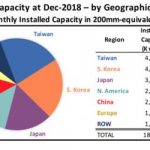

Physical Design for Secure Split Manufacturing of ICs

Semiconductors are not only critical to modern life, semiconductors are critical to National Security. Now that leading edge semiconductor foundries have left the United States one of the more pressing challenges is secure semiconductor manufacturing. This applies to all countries of course so let’s take a look at the International… Read More

Project Verification Planning for Analog Designs

Successful projects leverage the investment in comprehensive methodology and resource planning, covering design and analysis flows – that planning effort is especially important for functional verification.

The emergence of complex SoC designs for advanced automotive applications has led to a major focus on verification… Read More

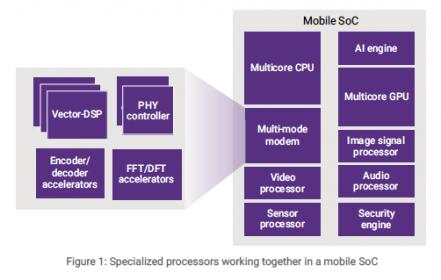

Goldilocks Solution for SOC Processors

SOC designers face choices when it comes to choosing how to implement algorithms in their designs. Moving them to hardware usually offers advantages of smaller area, less power and faster processing. Witness the migration of block chain hashing from CPUs to ASICs. However, these advantages can come with trade-offs. For one, … Read More

AI, Deep Learning, SystemC, UVM, PSS – DVCon Has it All

Today I had the pleasure to speak with Tom Fitzpatrick, TPC Chair for the DVCon conferenceand exhibition slated for February 25-28 in the heart of Silicon Valley – San Jose. Tom lives in Massachusetts, a place where I used to live and work at Wang Labs, back in the day before the PC and WordPerfect software ended Wang’s… Read More

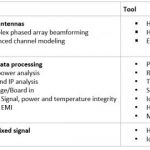

Accelerating 5G Innovation and Reliability Through Simulation and Advanced FinFET Design

In an ANSYS seminar held at DesignCon 2019, Dr. Larry Williams, ANSYS Director of Technology, outlined how 5G design innovation can be accelerated through simulation. He posited that 5G will become a general-purpose technology that affects an entire economy, drastically alter societies and unleash a cascade of complementary… Read More

Renaming and Refactoring in HDL Code

I’ve enjoyed my past discussions with Cristian Amitroaie, the CEO of AMIQ EDA, in which we covered their Design and Verification Tools (DVT) Eclipse Integrated Development Environment (IDE) and their Verissimo SystemVerilog Testbench Linter. Cristian’s descriptions of AMIQ’s products and customers have intrigued me. They… Read More

GLOBALFOUNDRIES Talks About Enabling Development of 5G ICs

5G is in the news again. Sprint has mounted a legal challenge against ATT, claiming that ATT is misleading people into believing that they already are offering 5G. While ATT is about to start testing of 5G, they have also sent out updates that causes customer phones to display 5GE when they are still on 4G LTE systems. The truth is that… Read More

Data Management Challenges in Physical Design

IC physical design (PD) teams face several challenges while dealing with tapeout schedules. With shrinking process nodes and stringent PPA targets, the complexity of physical design flows and EDA design tools has increased multifold. In addition the amount of design data that needs to be managed has also increased exponentially.… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center