Synopsys runs a “Industry verifies with Synopsys” lunch at each DVCon, which isn’t as cheesy as the title might suggest. The bulk of the lunch covers user presentations on their use of Synopsys tools which I find informative and quite open, sharing problems as much as successes. This year, Eamonn Quiqley, FPGA engineering manager… Read More

Electronic Design Automation

Surviving in the Age of Digitalization

There was an interesting keynote at DVCon last month. It was titled “Thriving in the Age of Digitalization” which introduced the concept of digital twins for design and production. It was presented by Fram Akiki who is a relative newcomer to EDA but has an interesting history so I will start there.

Fram and I got started in the semiconductor… Read More

Traceability and Design Verification Synergy

The IC design and verification process can be comprised of many independent point tools, or for more synergy you can have tools that work together by a more synergistic process. We’ve all heard the maxim, “Work smarter, not harder.” A white paper just came out from Methodics on a smarter approach, Traceability… Read More

Silvaco WEBINAR: Nanometer Library Characterization Challenges and Solutions

As you may know, Silvaco has done some very clever acquisitions to fuel their unprecedented growth over the last five years. We have a wiki that tracks EDA Mergers and Acquisitions, Silvaco included, and it is the most viewed wiki on SemiWiki.com with 102,005 views thus far.

Silvaco acquired Nangate in March of 2018. NanGate got … Read More

Three things you should know about designHUB!

One of the key growth areas for the semiconductor ecosystem is IP which of course includes IP related EDA software. In May of 2017 design management/collaboration expert (one of my personal favorite EDA companies) ClioSoft announced designHUB[SUP]®[/SUP] for IP management and re-use. Using designHUB, semiconductor companies… Read More

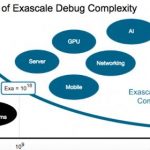

Synopsys Tackles Debug for Giga-Runs on Giga-Designs

I think Synopsys would agree that they were not an early entrant to the emulation game, but once they really got moving, they’ve been working hard to catch up and even overtake in some areas. A recent webinar highlighted work they have been doing to overcome a common challenge in this area. Being able to boot a billion-gate design, … Read More

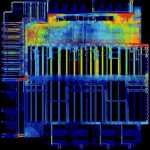

Webinar: Addressing Multiphysics Challenges in 7nm FinFET Designs

EDA is big on growth through acquisition, being acquired many times throughout my career I know this by experience. In fact, we have a wiki that tracks EDA Mergers and Acquisitions and it is the most viewed wiki on SemiWiki.com with 101,918 views thus far.

In March of 2017 ANSYS acquired CLK Design Automation which did timing variation… Read More

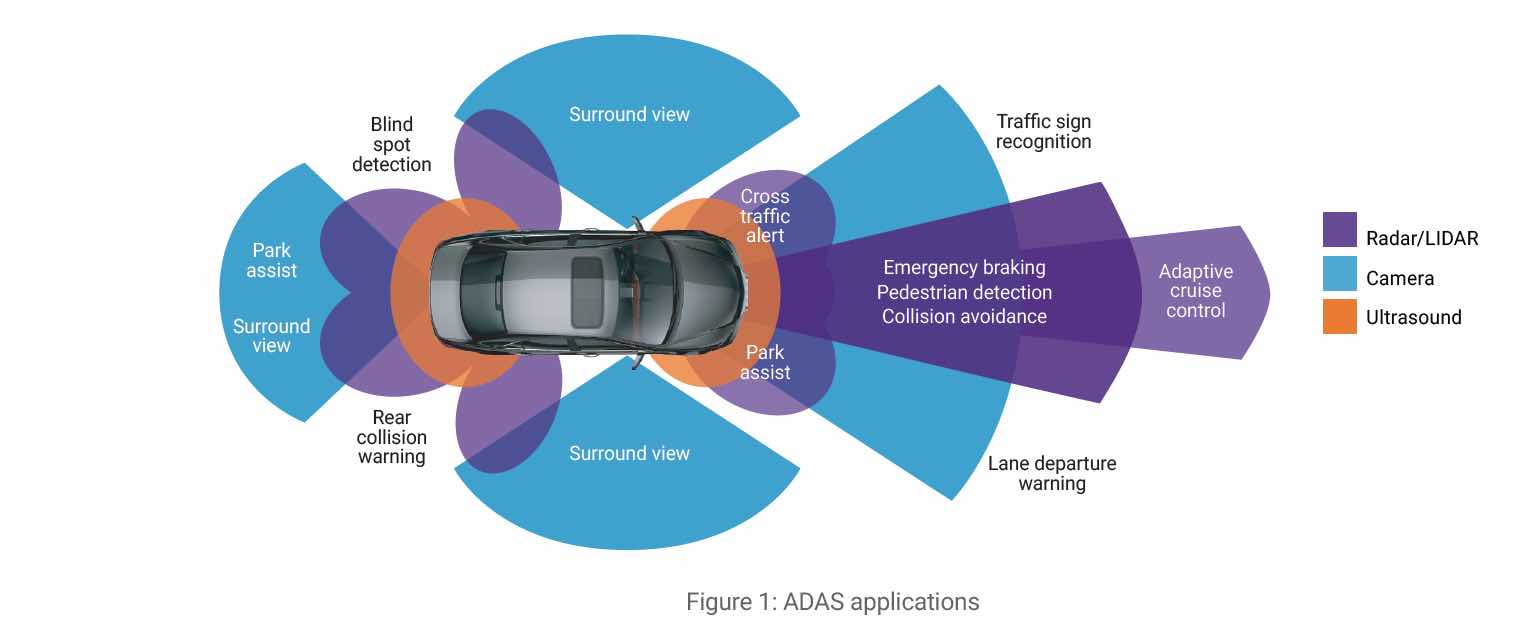

Accelerating SOC Development for Automobile Applications

No area of electronics is moving faster than automotive semiconductors. Everyone has been talking about the increasing electronics content of automobiles for decades. With Advanced Driver Assistance System (ADAS) and autonomous driving becoming a reality the pace has picked up even more. These new designs combine just about… Read More

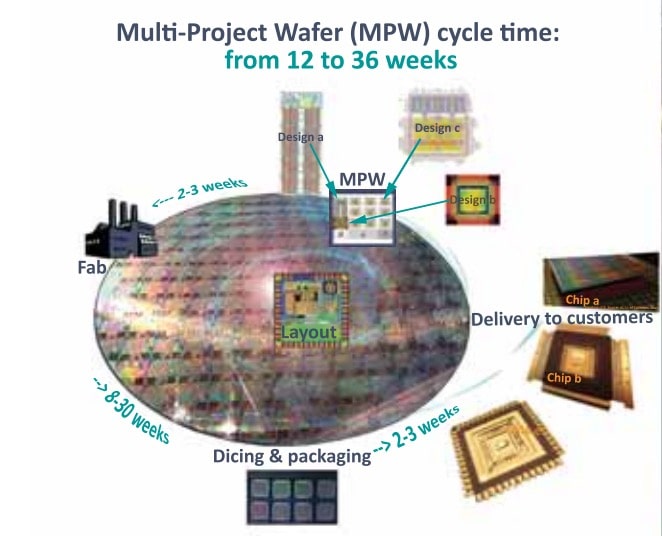

Ultra low-power Analog Design using a Multi-Project Wafer approach

On SemiWiki we often talk about bleeding-edge technology like 7nm, 5nm or even 3nm, but for analog IC designs there’s a low-cost alternative to getting your ideas validated and prototyped without taking out a multi-million dollar loan, and that’s through the use of Multi-Project Wafers (MPW). Starting with a mature… Read More

Data Centers and AI Chips Benefit from Embedded In-Chip Monitoring

Webinars are a quick way to come up to speed with emerging trends in our semiconductor world, so I just finished watching an interesting one from Moortec about the benefits of embedded in-chip monitoring for Data Center and AIchip design. My first exposure to a data center was back in the 1960s during an elementary school class where… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center