Recently, Daniel Nenni blogged on the presentation Wally Rhines gave at #56th DAC. Daniel provided a great summary, but I want to dive into a portion of the presentation in more detail. I love Wally’s presentations, but sometimes you cannot absorb the wealth of information he provides when you initially see it. It’s… Read More

Electronic Design Automation

TSMC in the Cloud Update #56thDAC 2019

During my Taiwan visit, prior to Las Vegas, I was fortunate to spend time with Willy Chen and Vivian Jiang to prepare for the cloud panel I moderated at #56thDAC. Willy and Vivian are part of the ever-important Design Infrastructure Marketing Division of TSMC, which includes the internal and external cloud efforts. TSMC first announced… Read More

#56DAC – What’s New with Custom Design Platform

TSMC attends DAC every year and they do something very savvy, it’s a theatre where they invite all of their EDA and IP partners to present something of interest, followed by a drawing for a prize. At the end of the day they even have a nice prize, like a MacBook Air, which I didn’t win. On Wednesday I watched Dave Reed of Synopsys… Read More

The Complexity of Block-Level Placement @ 56thDAC

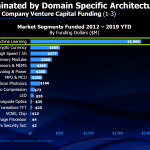

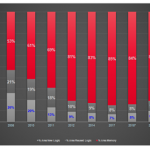

The recent Design Automation Conference in Las Vegas was an indication of how the electronics industry is evolving. In its formative years, DAC was focused on the fundamental algorithms emerging from academic research and industrial R&D, that enabled the continuation of the Moore’s Law complexity curve. (Indeed, the… Read More

Wally Rhines Keynote @ #56thDAC!

One of the perks of blogging on SemiWiki is the events you get to attend for FREE and the amazing people you get to meet and Wally Rhines is certainly one of those people. You will not find a more intelligent, innovative, and genuinely nice group of people in my experience. Having traveled the world meeting thousands of people I can tell… Read More

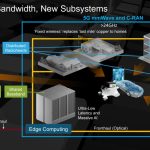

Cadence on 5G Intelligent System Design #56thDAC

As much as I love all EDA vendors I must say Cadence did the best DAC this year. Great booth, great location, excellent content, and of course a great party. The 5G presentation in the Cadence booth by Ian Dennison was of great interest to me as I am still trying to wrap my head around this whole 5G thing. I was able to meet with Ian privately… Read More

#56DAC – Machine Learning and its impact on the Digital Design Engineer

Tuesday for lunch at #56DAC I caught up to the AI/ML experts at the panel discussion hosted by Cadence. Our moderator was the affable and knowledgable Prof. Andrew Kahng from UC San Diego. Attendance was good, and interest was quite high as measured by the number of audience questions. I learned that EDA tools that use heuristics… Read More

#56DAC – Panel Discussion: Closing Analog and Mixed-Signal Verification in 5G, HPC and Automotive

Monday afternoon at #56DAC I enjoyed attending a luncheon panel discussion from four AMS experts and moderator, Prof. Georges Gielen, KU Leuven. I follow all things SPICE and this seemed like a great place to get a front-row seat about the challenges that only a SPICE circuit simulator can address. Here’s a brief introduction… Read More

Cadence Releases Enterprise-Level FPGA Prototyping

Big prototyping hardware is essential to modern firmware and software development for pre-silicon, multi-billion gate hardware. For hardware verification it complements emulation, running fast enough for realistic testing on big software loads while still allowing fast-switch to emulation for more detailed debug where… Read More

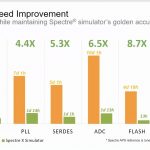

Parallel SPICE Circuit Simulator Debuts

In EDA the most successful companies will often re-write their software tools in order to add new features, improve accuracy, increase capacity and of course, shorten run times. For SPICE circuit simulators we typically look at several factors to see if a new tool is worth a look or not:

- Netlist compatibility

- Model support

- Foundry

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era