I moved from real layout work to management so I had little or no “hands-on” layout in my responsibility but I was very close to my team challenges in all 5 locations. During my 13 years in PMC Sierra I was involved in many initiatives some technical and some in developing relations with vendors. The biggest difference was that MOSAID was eager to get media coverage and PMC was very secretive of the tools or vendors it used. In this period I had to sign a lot of personal NDA as software companies wanted to ensure their ideas are kept confidential.

I moved from real layout work to management so I had little or no “hands-on” layout in my responsibility but I was very close to my team challenges in all 5 locations. During my 13 years in PMC Sierra I was involved in many initiatives some technical and some in developing relations with vendors. The biggest difference was that MOSAID was eager to get media coverage and PMC was very secretive of the tools or vendors it used. In this period I had to sign a lot of personal NDA as software companies wanted to ensure their ideas are kept confidential.

It started with integration of our microprocessor division from the former QED  company. They were designing processors and the rest of PMC SoCs. We were using a simple TSMC process and they were using a “fancy” high-end foundry that offered additional speed and had an easy process migration road-map. The task was to unify the PDK, the tools and the efforts in such way that

company. They were designing processors and the rest of PMC SoCs. We were using a simple TSMC process and they were using a “fancy” high-end foundry that offered additional speed and had an easy process migration road-map. The task was to unify the PDK, the tools and the efforts in such way that

our teams can provide IP to microprocessors for fast interfaces and we may use their Cores for our needs. In 90 nm we developed an internal LAMBDA process between the 2 flavours, the worst common denominator!!! A very challenging and interesting initiative that enabled me to use my Motorola experience. Working long distance with Sinan Doluca and his team was a challenging task but became a long time friendship. As a processor is very dependent on the quality of Register Files,

Multipliers, Adders, we started to work with vendors to find a Datapath friendly tool.

Multipliers, Adders, we started to work with vendors to find a Datapath friendly tool.

Sycon had a silicon compiler for Datapath as they were coming from Intel microprocessor group and CAD. They developed a new cell level solution to compliment the initial block level software. I was a very closed reviewer of all these developments and at one DAC the conference electrician had to wait until Jack Feldman finished to show me the “unreleased features” at 5 PM Thursday evening! That was exiting !!! At the same time Cadabra, who had a silicon compiler for cells, was trying to move up to block level but was not ready yet. I decided that the best option will be to work with Pulsic. They had a full custom/digital place and route solution that could add some Datapath options for microprocessor needs. I started to talk

to  Dave Noble and Jeremy Birch to add features like global signals pre-placement and device placement based on “pre-routes”. We managed to get the features implemented but by that time PMC decided to stick with a single vendor so we lost the opportunity to use PULSIC. However LAMBDA flow required a lot of DRC fixing so we got Sagantec SiFix at that time, see my previous article.

Dave Noble and Jeremy Birch to add features like global signals pre-placement and device placement based on “pre-routes”. We managed to get the features implemented but by that time PMC decided to stick with a single vendor so we lost the opportunity to use PULSIC. However LAMBDA flow required a lot of DRC fixing so we got Sagantec SiFix at that time, see my previous article.

One of the big issues CADENCE had was that users were reluctant to new tools, most of them were using Virtuoso L, not even the VXL. In top of VXL Cadence bought a few companies (Neolinear, CCT, QDesign,

etc.) with very powerful tools that had introduction issues. The main reason was high introductory price. Each of the licenses with advance features costs a lot of money and nobody was planning to use them for a very long time at once (CPU time)… For a 2 hours routing every week you needed to prove that 150K tool increases productivity and it can be quantified. After many discussion with Cadence I shared with them the tokens based system, an idea coming from Michael Reinhardt former CEO of Rubicad. You can pool together all the expensive licenses like VCP, VCR, VLM, MODGEN, etc. and call it … GXL. Each of these licenses has a now an equivalent value in tokens. Lets say 20 tokens for a global router, 30 for VLM, 6 for MODGEN. This way if you think you know what the team needs you purchase 60 tokens for a year and you can use at the same time (CPU controlled) 2 VLM license or 3 global routers or 10 MODGEN. Once you

etc.) with very powerful tools that had introduction issues. The main reason was high introductory price. Each of the licenses with advance features costs a lot of money and nobody was planning to use them for a very long time at once (CPU time)… For a 2 hours routing every week you needed to prove that 150K tool increases productivity and it can be quantified. After many discussion with Cadence I shared with them the tokens based system, an idea coming from Michael Reinhardt former CEO of Rubicad. You can pool together all the expensive licenses like VCP, VCR, VLM, MODGEN, etc. and call it … GXL. Each of these licenses has a now an equivalent value in tokens. Lets say 20 tokens for a global router, 30 for VLM, 6 for MODGEN. This way if you think you know what the team needs you purchase 60 tokens for a year and you can use at the same time (CPU controlled) 2 VLM license or 3 global routers or 10 MODGEN. Once you

release the licence somebody else can reuse the tokens for their needs by calling different tools from the pool. I cannot claim that GXL was my idea, but I was closely involved with Mike Stroobandt and benefited for the following years like many of you.

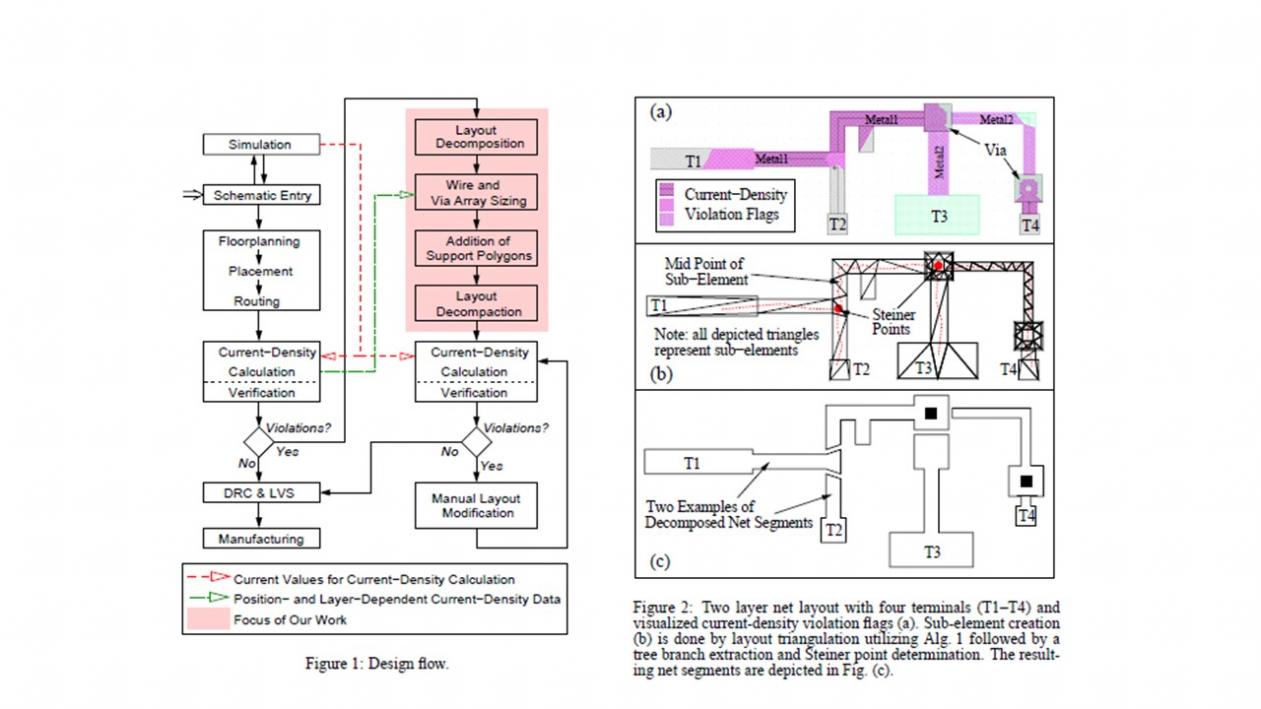

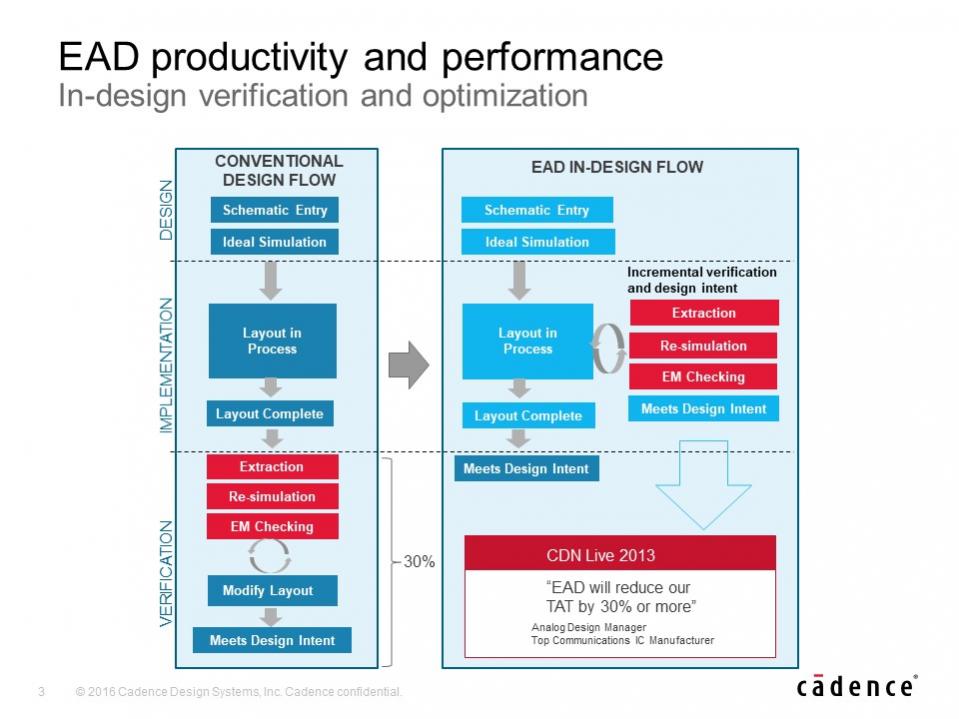

Saying you want Electromigration tools is a good start but not enough. We did solve the issue in PMC in 2002 but this was a post layout solutionand I wanted an “online as you go” option. I decided that the only way to make this topic popular is to socialise the concept with my friends in the industry and the software world. I built a short PPT and with each occasion I presented to Synopsys, Cadence, Mentor, ClioSoft, etc… From sales people to architects, from technical marketing to implementation guys.

I even spoke with university professors to push it. One of them, Jens Lienig, a German professor presenting in DAC panels, provided me with his papers on Electromigration. Apparently I was not the only one asking for it so Cadence Vinod Kariat and David White promised to do something about it, the problem they saw was to find capable drivers to take over such initiative. I proposed my old friends  Michael McSherry & Ed Fisher. Michael was the former marketing manager for Calibre and Ed was the former engineering manager for IC Station, now both in Cadence. To my surprize the following DAC I was invited in a booth and meet both of them, ready to take over the challenge. We spent some time to go over the idea and the basic features. I was interested to follow-up but PMC did not agree to be part of Alpha or Beta testing so I did it from the sidelines… By the time theElectrically Aware Design or as you know it EAD, was ready for public use I was out of PMC. I enjoy all the demos and new developments on this tool as I consider it a revolutionary, by improving design and layout in full custom world in all technologies down to 7 nm.

Michael McSherry & Ed Fisher. Michael was the former marketing manager for Calibre and Ed was the former engineering manager for IC Station, now both in Cadence. To my surprize the following DAC I was invited in a booth and meet both of them, ready to take over the challenge. We spent some time to go over the idea and the basic features. I was interested to follow-up but PMC did not agree to be part of Alpha or Beta testing so I did it from the sidelines… By the time theElectrically Aware Design or as you know it EAD, was ready for public use I was out of PMC. I enjoy all the demos and new developments on this tool as I consider it a revolutionary, by improving design and layout in full custom world in all technologies down to 7 nm.

During my PMC time I I worked with many companies to help them bring new ideas to market. From ClioSoft Laker 4, to Cadence EAD, from Mentor Graphics Calibre CB to Pulsic Animate, I always tried to push forward automation to make layout designers work easier and less monotone. I reviewed a lot of specifications, I was part of products reviews and demos “for your eyes only”, I had (and still have) a lot of fun.

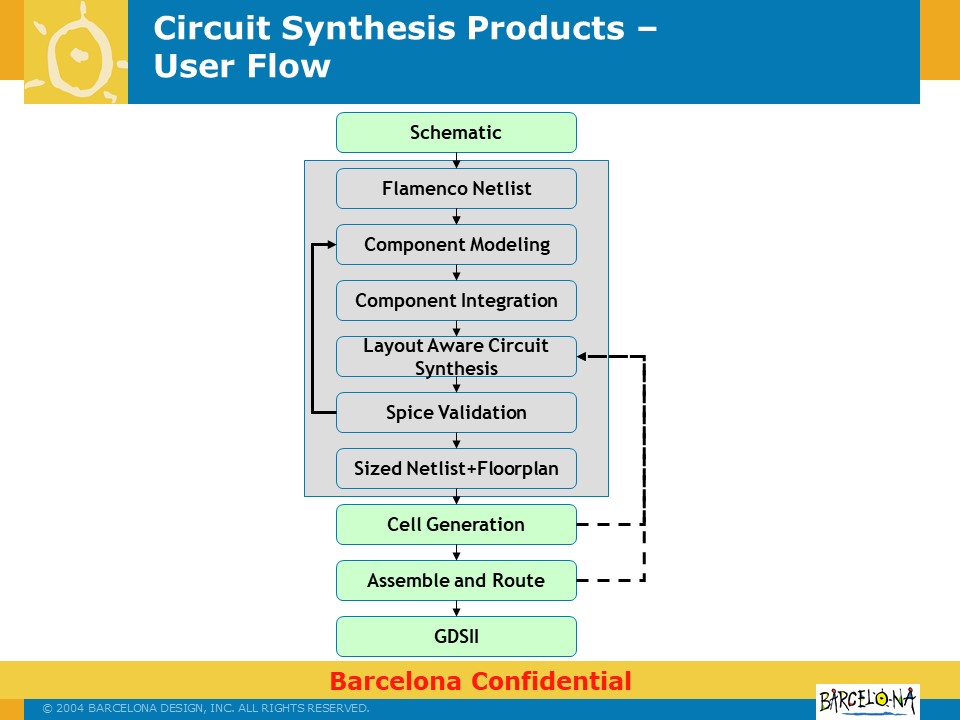

I had endless debates with John Stabenow for complex features and demos (some in Cadence and some in Synopsys), Jeremiah Cessna for MODGEN with PCELLS or not, Olivier Arnaud for VXL grouping features, Philippe Hurat for advance nodes automation, etc. This names are only from Cadence and I have to thank Deana Spencer for enabling me to talk to a lot of internal architects and developers… I had similar talks with Mentor, Synopsys and many small startups to help them translate their vision into something we, the users, can relate… Many time things moved forward or changed direction, sometimes they disappeared like Cadabra or Cosmos. I am sorry that Mar Hershenson did not succeed to bring Barcelona Design or next solutions to success. I considered it a good revolution in automating layout for “template

circuits”. I was lucky to meet all these industry experts as my book was used in many cases to explain concepts or argue in flow debates.

We looked closely at Accelicon AVP with Mahesh Guruswamy help and Bindkey DRC cleaning tools with

Micha Oren, but by the time were ready to buy their tools the companies were bought and all got cancelled. Mixed Signal Layout group liked automation so much that with VCP + VCR Stephane Leclerc rebuilt the ACPD flow in 65 nm and we prepared a paper for CDN Live in 2008.

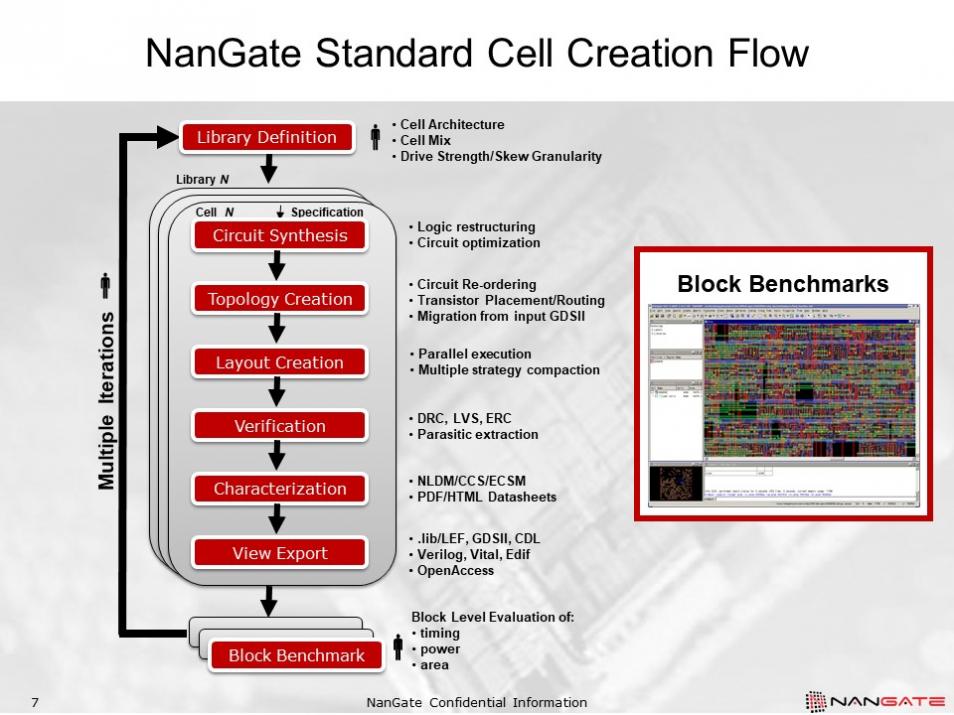

By 2012 we moved to a new technology node so mixed signal team decided to use automation at maximum by using schematic driven P & R. We needed a high speed library for the digital parts of our analog blocks. We ended up with almost 2000 cells “wish list”. We had 2 option, by hand or automated, but as this was never done at this level in PMC the risk of effort/schedule overrun was big in both cases. Based on our Return On Investment (ROI) presentation the manual solution was 4x the price of automation so it looked worthy. We used2 layout designers, 1 CAD and 1 circuit designer and created in 2.5 months 2000 high-performance standard cells layout in 28 nm running between 1.6 to 6.2 GHzspeed in post layout simulation. Special appreciation for Jens C. Michelsen the COO of Nangate who agreed to a short license “lease” and sent us a great trainer. In one week the team was able to tackle all tool issues and we were able to produce. The team finished 15 days ahead of plan and the final ROI including the tool price, training and ramp up went to 5x cheaper than hand crafted library.

By 2012 we moved to a new technology node so mixed signal team decided to use automation at maximum by using schematic driven P & R. We needed a high speed library for the digital parts of our analog blocks. We ended up with almost 2000 cells “wish list”. We had 2 option, by hand or automated, but as this was never done at this level in PMC the risk of effort/schedule overrun was big in both cases. Based on our Return On Investment (ROI) presentation the manual solution was 4x the price of automation so it looked worthy. We used2 layout designers, 1 CAD and 1 circuit designer and created in 2.5 months 2000 high-performance standard cells layout in 28 nm running between 1.6 to 6.2 GHzspeed in post layout simulation. Special appreciation for Jens C. Michelsen the COO of Nangate who agreed to a short license “lease” and sent us a great trainer. In one week the team was able to tackle all tool issues and we were able to produce. The team finished 15 days ahead of plan and the final ROI including the tool price, training and ramp up went to 5x cheaper than hand crafted library.

Another proof that automation and not manuallabour is the future!

More to come… stay put on Sankalp contributions…

Dan Clein

Share this post via:

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!