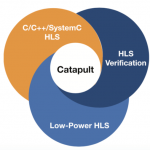

I’ve talked before about Mentor’s work in high-level synthesis (HLS) and machine learning (ML). An important advantage of HLS in these applications is its ability to very quickly adapt and optimize architecture and verify an implementation to an objective in a highly dynamic domain. Design for automotive applications – for … Read More

Electronic Design Automation

Virtuoso Adapts to Address Cyber Physical Systems

LIDAR is a controversial topic, with even Elon Musk weighing in on whether it will ever be feasible for use in self driving cars. His contention is that the sensors will remain too expensive and potentially be unreliable because of their mechanical complexity. However, each of the sensors available for autonomous driving have … Read More

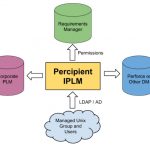

IP Lifecycle Management and Permissions

My first professional experience with computers and file permissions was at Intel in the late 1970s, where we used big iron IBM mainframes located far away in another state, and each user could edit their own files along with browse shared files from co-workers in the same department. I saw this same file permission concept when … Read More

Taking the Pain out of UVM

If you are interested in gaining a deeper understanding of the many ways you can leverage the Universal Verification Methodology (UVM), Breker Verification Systems has gone to a lot of effort to put that information at your fingertips.

A technical subcommittee of Accellera voted to establish the UVM in December 2009. UVM was based… Read More

The Wild, Wild SEMICON West TechTALK – Joe Costello Speaks Out

On July 9, 2019, I attended the TechTALK session hosted by Dave Kelf of Breker Systems, Inc. titled, “Applied AI in Design-to-Manufacturing.” I was happy to hear what Dave had put together for this since it is a topic I am keenly interested in and because I have known Dave personally through music and charitable activities we have … Read More

5G and V2X

Amid the glamor of autonomous vehicles and hot new ADAS features, communication between vehicles and other vehicles, pedestrians, cyclists or infrastructure, generally labeled V2X, doesn’t get as much press, perhaps because adoption is still pretty early or because it’s technology under the hood (quite literally) and therefore… Read More

#DAC56 – Optimizing Verification Throughput for Advanced Designs in a Connected World

It was the final day of DAC56 and my head was already spinning from information overload after meeting so many people and hearing so many presentations, but I knew that IC functional verification was a huge topic and looming bottleneck for many SoC design teams, so I made a last-minute email request to attend a luncheon panel discussion… Read More

The Flash and the Taiwan ESD Seminar!

During my trip through Asia last week I attended the Taiwan ESD Workshop. Hsinchu is densely populated with some of the smartest semiconductor people in the world so it is well worth the trip, absolutely. As it turns out ESD is one of the top concerns in semiconductor design and manufacture. The current rule based and simulation … Read More

Synopsys and Synaptics Talk About Securing the Connected Home

Like many people, I have been adding automation to my home, and the number of connected devices I use has slowly but steadily increased. These include light bulbs, cameras, switches, a thermostat, a voice assistant, etc. Between them, they know when I am home or away, and have the ability to record images and sound. In addition to … Read More

PSS and Reuse: Great Solution But Not Hands-Free

If you’re new to PSS you could be forgiven for thinking that it automagically makes stimulus reusable, vertically from IPs to systems, horizontally between derivatives and between hardware-based and software-based testing. From a big-picture point of view these are certainly all potential benefits of PSS.

What PSS does provide… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era