It seems every day we see a new article (or ten) on autonomous driving. It is an especially hot topic, and it will happen someday. For now, we can dream about it, and many people are working on it. But for the present, the technology in a car that commands my attention is audio. I’ve been a musician since 4th grade. I still perform occasionally… Read More

Electronic Design Automation

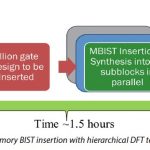

Can a hierarchical Test flow be used on a flat design?

It is pretty common for physical layout to work from a flattened hierarchy for blocks or even full chips, even though the front-end design starts with a hierarchical representation. This was not always the case. Way back when, the physical layout matched the logical hierarchy during the design process. Of course, this led to all… Read More

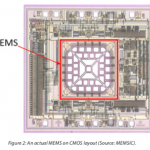

Mentor-Tanner Illuminate MEMS Sensing, Fusion

I enjoy learning and writing about new technologies closely connected to our personal and working lives (the kind you could explain to your Mom or a neighbor). So naturally I’m interested in AI, communication and security as applied to the home automation, transportation, virtual, augmented and mixed reality, industry and so… Read More

Accelerate Your Early Design Recon

A product launch nowadays demands shorter runway. SoC designers challenges are not so much in facing the unavailability of proven design capture methodologies or IP’s that could satisfy their product requirements, but more so in orchestrating the integration of all those components to deliver the targeted functionalities… Read More

Webinar: Designing Complex SoCs and Dealing with Multiple File Formats

In SoC design it’s all about managing complexity through modeling, and the models that make up IC designs come in a wide range of file formats like:

- Transistor-level , SPICE

- Interconnect parasitics, SPEF

- Gate and RTL, Verilog, VHDL

Even with standard file formats, designers still have to traverse the hierarchy to find out… Read More

Tortuga Webinar: Ensuring System Level Security Through HW/SW Verification

We all know (I hope) that security is important so we’re willing to invest time and money in this area but there are a couple of problems. First there’s no point in making your design secure if it’s not competitive and making it competitive is hard enough, so the great majority of resource and investment is going to go into that objective.… Read More

Adding CDM Protection to a Real World LNA Test Case

In RF designs Low Noise Amplifiers (LNA) play a critical role in system operation. They simultaneously need to be extremely sensitive and noise free, yet also must be able to withstand strong signal input without distortion. LNA designers often struggle to meet device performance specifications. Their task is further complicated… Read More

GPU-Powered SPICE – Understanding the Cost

To deploy a GPU-based SPICE solution, you need to understand the costs involved. To get your hands on this new report analyzing this specific issue, all you need to do is attend Empyrean’s upcoming webinar, “GPU-Powered SPICE: The Way Forward for Analog Simulation,” which will be held on Thursday, August 8, 2019, at 10:00 am (PDT).… Read More

56th DAC – In Depth Look at Analog IP Migration from MunEDA

Every year at DAC, in addition to the hubbub of the exhibit floor and the relatively short technical sessions, there are a number of tutorials that dive in depth into interesting topics. At the 56th DAC in Las Vegas this year, MunEDA offered an interesting tutorial on Analog IP migration and optimization. This is a key issue for large… Read More

IP Provider Vidatronic Embraces the ClioSoft Design Management Platform

Having worked at several semiconductor intellectual property (SIP) companies, I know how important it is to have a strong design data management platform for tracking the development and distribution of SIP products. Everyone doing semiconductor design should care about design data management. But for an IP company, it is … Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era