I don’t look at the RTL power estimation topic too often these days, so I was interested to see that ANSYS still has a very strong position in this area. Qualcomm is using PowerArtist on one of the most demanding modern applications – mobile GPU power gaming. Mobile gaming heavily loads the GPU, so any optimization in that area will … Read More

Electronic Design Automation

Interview with Altair CTO Sam Mahalingam

In this interview we talk with Sam Mahalingam, chief technology officer at Altair, about gaining a competitive edge with software that’s built to handle high-throughput workloads like chip design and electronic design automation (EDA). Altair is a global technology company providing solutions in product development, high-performance… Read More

CEO Interview: John O’Donnel of yieldHUB

Let me introduce John O’Donnell, CEO of yieldHUB. After earning a degree in microelectronics John spent 18 years at Analog Devices before founding yieldHUB in 2005. If anybody knows yield it is Analog Devices having shipped billions upon billions of chips, absolutely.

SemiWiki will be digging deeper into the technology… Read More

Nobody Ever Lost Their Job for Spending too Much on Hardware Verification, Did They?

A paper was published last month on the Acuerdo Consultancy Services website authored by Joe Convey of Acuerdo and Bryan Dickman of Valytic Consulting. Joe and Bryan spent combined decades in the Semi and EDA World which means they have a great understanding of hardware bugs first hand, absolutely.

Here is a quick summary… Read More

Why Go Custom in AI Accelerators, Revisited

I believe I asked this question a year or two ago and answered it for the absolute bleeding edge of datacenter performance – Google TPU and the like. Those hyperscalars (Google, Amazon, Microsoft, Baidu, Alibaba, etc) who want to do on-the-fly recognition in pictures so they can tag friends in photos, do almost real-time machine… Read More

How to Grow with Poise and Grace, a Tale of Scalability from ClioSoft

ClioSoft published a white paper recently entitled Best Practices are the Foundations of a Startup. The piece discusses the needs and challenges associated with building a scalable infrastructure to support growth.

Before I get into more details on ClioSoft’s white paper, I would offer my own experience on this topic – the need… Read More

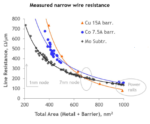

Design Technology Co-Optimization (DTCO) for sub-5nm Process Nodes

Summary

Design Technology Co-Optimization (DTCO) analysis was pursued for library cell PPA estimates for gate-all-around (GAA) devices and new metallurgy options. The cell design and process recommendations are a bit surprising.

Introduction

During the “golden years” of silicon technology evolution that applied Dennard… Read More

DVCon 2020 Virtual Follow-Up Conference!

As most of you know DVCon 2020 was our first conference to be cut short by the Pandemic. SemiWiki bloggers Bernard Murphy, Mike Gianfagna, and I were there with full schedules but at the last minute it was called off. It really was an eerie feeling, the emptiness of it all.

The rest of our EDA live events followed suit and went virtual … Read More

The Moving Target Known as UPF

As if engineers did not have enough difficulty just getting everything right so that their designs are implemented functionally correct, the demands of lowering power consumption require changes that can affect functionality and verification. Techniques such as power gating, clock gating, mixed supply voltage, voltage … Read More

Cadence Adds “Always On” to vManager Verification Management with Distributed and Cloud Access

Cadence vManager™ Verification Management provides what the company describes as metric-driven signoff. Anyone who has been through the tapeout process for a complex SoC knows the perils of verification sign-off. How much of the chip has been verified? What’s left to do? Will all be ready when the tapeout deadline arrives? … Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era