Artificial Intelligence (AI) and Machine Learning (ML) are becoming more and more commonplace in our world. We have Siri, Alexa and Google Assistant that understand our voice commands. Vision systems that recognize objects are used for facial recognition, autonomous driving, medical, geographical and many other applications.… Read More

Electronic Design Automation

DAC Panel: Cadence Weighs in on AI for EDA, What Applications, Where’s the Data?

DAC was full of great panels, research papers and chip design stories this year, the same as other years. Being a virtual show, there were some differences of course. I’ve heard attendance was way up, allowing a lot more folks to experience the technical program. This is likely to be true for a virtual event. I’m sure we’ll see more… Read More

#57DAC – Panel Discussion of High Level Synthesis

Presenters took a trip down memory lane at DAC this year by having a panel discussion on HLS (High Level Synthesis) spanning from 1974 to 2020, and that time period aligns with when I first graduated from the University of Minnesota in 1978, starting chip design at Intel, then later transitioning into EDA companies by 1986. Marilyn… Read More

Low Power and RISC-V Talks at DAC2020, Hosted by Mentor

I’m going to get to low power and RISC-V, but first I’m trying out virtual DAC this year. Seems to be working smoothly, aside from some glitches in registration. But maybe that’s just me – I switched email addresses in the middle of the process. Some sessions are live, many pre-recorded, not quite the same interactive experience… Read More

A SoC Design Flow With IP-XACT

Taping out a SoC is never easy. The physical dimensions of the chip often belie the work which has been done to get to the tapeout stage. And it is still not a done deal as the hardware and software development teams await the arrival of the test chip from the foundry to complete the post silicon bring-up and validation. The pressure on… Read More

Synopsys Webinar: A Comprehensive Overview of High-Speed Data Center Communications

High-speed communication is a critical component for many applications, most notably in the data center. The serializer/deserializer physical interface, or SerDes PHY is the backbone of many different forms of high-speed communication for this application. Use cases include on chip, between chips, between boards and racks… Read More

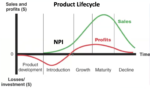

How yieldHUB Helps Bring a New Product to Market

Collecting and analyzing semiconductor test data is a subject that holds a special place for me. Developing a factory data collection and analysis system was my first job out of school. The company was RCA, and the factories were in Findlay, Ohio (analog/mixed signal) and West Palm Beach, Florida (digital). There was a pilot… Read More

The Polyglot World of Hardware Design and Verification

It has become a cliché to start a blog post with a cliché, for example “Chip designs are forever getting larger and more complex” or “Verification now consumes 60% of a project’s resources.” Therefore, I’ll open this post with another cliché: “Designers need to know only one language, but verification engineers must know many.”… Read More

How About a Faster Fast SPICE? Much Faster!

When Analog FastSPICE was first introduced in 2006 it changed the landscape for high performance SPICE simulation. During the last 14 years it has been used widely to verify advanced nanometer designs. Of course, since then the most advanced designs have progressed significantly, making verification even more difficult. Just… Read More

Accelerating High-Performance Computing SoC Designs with Synopsys IP

Semiconductor IP is one of the most talked about topics on SemiWiki. Always has been, always will be. Synopsys is also one of the most talked about topics on SemiWiki and IP is a very big part of that, absolutely.

After reading Eric Esteve’s latest IP Report I Googled around and found some interesting things. First, I found a Brief History… Read More

Flynn Was Right: How a 2003 Warning Foretold Today’s Architectural Pivot