You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 58

[name] => Defacto Technologies

[slug] => defacto-technologies

[term_group] => 0

[term_taxonomy_id] => 58

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 34

[filter] => raw

[cat_ID] => 58

[category_count] => 34

[category_description] =>

[cat_name] => Defacto Technologies

[category_nicename] => defacto-technologies

[category_parent] => 157

[is_post] =>

)

WP_Term Object

(

[term_id] => 58

[name] => Defacto Technologies

[slug] => defacto-technologies

[term_group] => 0

[term_taxonomy_id] => 58

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 34

[filter] => raw

[cat_ID] => 58

[category_count] => 34

[category_description] =>

[cat_name] => Defacto Technologies

[category_nicename] => defacto-technologies

[category_parent] => 157

[is_post] =>

)

“For more than 18 years, we never stopped innovating at Defacto. We are aware of EDA Mantra “Innovate or Die!”. Innovation is in our DNA, and we never stopped adding new automated capabilities to the SoC design community to help facing complexity and cost challenges, which increase every year.”

Before founding Defacto… Read More

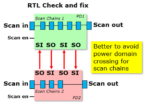

In the early days of Atrenta I met with Ralph Marlett, a distinguished test expert with many years of experience at Zuken and Recal Redac. He talked me into believing we could do meaningful static analysis for DFT-friendliness at RTL. His work with us really opened my eyes to the challenges that test groups face in integrating their… Read More

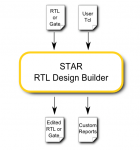

I’ve talked before about how Defacto provides a platform for scripted RTL assembly. Kind of a rethink of the IP-XACT concept but without need to get into XML (it works directly with SV), and with a more relaxed approach in which you decide what you want to automate and how you want to script it.

They’re hosting a webinar on May 28th 10-11am… Read More

I’ve talked with Defacto on and off for several years – Chouki Aktouf (CEO) and Bastien Gratreaux (Marketing). I was in a similar line of business back in Atrenta. Now I’m just enjoying myself, I’ve written a few blogs for them. I’ll confess I wondered why they wouldn’t struggle with the same problems we’d had. Script-driven RTL editing,… Read More

DeFacto and their STAR technology are already quite well known among those who want to procedurally apply edits to system-level RTL. I’m not talking here about the kind of edits you would make with your standard edit tools. Rather these are the more convoluted sort of changes you might attempt with Perl (or perhaps Python these days).… Read More

For the devices we build today, design and implementation are unavoidably entangled. Design for low-power, test, reuse and optimized layout are no longer possible without taking implementation factors into account in design, and vice-versa. But design teams can’t afford to iterate indefinitely between these phases, so they… Read More

It is self-evident that large systems of any type would not be possible without hierarchical design. Decomposing a large system objective into subsystems, and subsystems of subsystems, has multiple benefits. Smaller subsystems can be more easily understood and better tested when built, robust 3[SUP]rd[/SUP] party alternatives… Read More

To paraphrase an Austen line, it is a truth universally acknowledged that implementation, power intent and design hierarchy don’t always align very well. Hierarchy is an artifact of legacy structure, reuse and division of labor, perhaps well-structured piecewise for other designs but not necessarily so for the design you now… Read More

Themes in EDA come in waves and a popular theme from time to time is RTL signoff. That’s a tricky concept; you can’t signoff RTL in the sense of never having to go back and change the RTL. But the intent is still valuable – to get the top-level or subsystem-level RTL as well tested as possible, together with collateral data (SDC, UPF, etc)… Read More

As a 30+ year semiconductor veteran I can tell you with 100% certainty that start-ups are the lifeblood of EDA. The mantra is “Innovate or Die!” and that is exactly what Defacto is doing. After more than 10 years of innovating in Design for Test at RTL, Defacto is now offering a complete EDA solution based on generic EDA… Read More