Cadence has done a good job of keeping up with the needs of analog RF designs. Of course, the term RF used to be reserved for a thin slice of designs that were used specifically in RF applications. Now, it covers things like SerDes for networking chips that have to operate in the gigahertz range. Add that to the trend of combining RF and… Read More

Author: Tom Simon

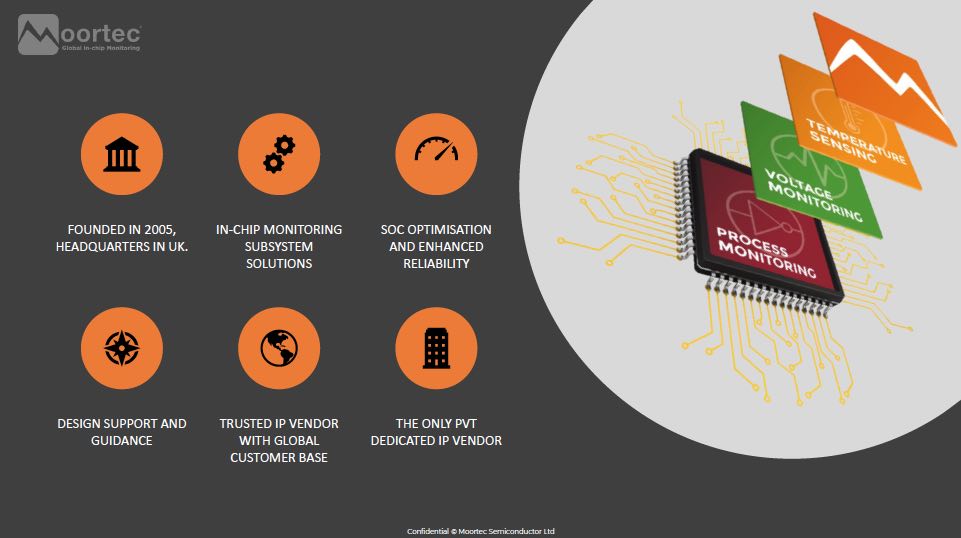

A Smart Way for Chips to Deal with PVT Issues

We have all become so used to ‘smart’ things that perhaps in a way we have forgotten what it was like before many of the things we use day to day had sensors and microprocessors to help them respond to their environment. Cars are an excellent example. It used to be commonplace to run down your battery by leaving your lights on. Now cars … Read More

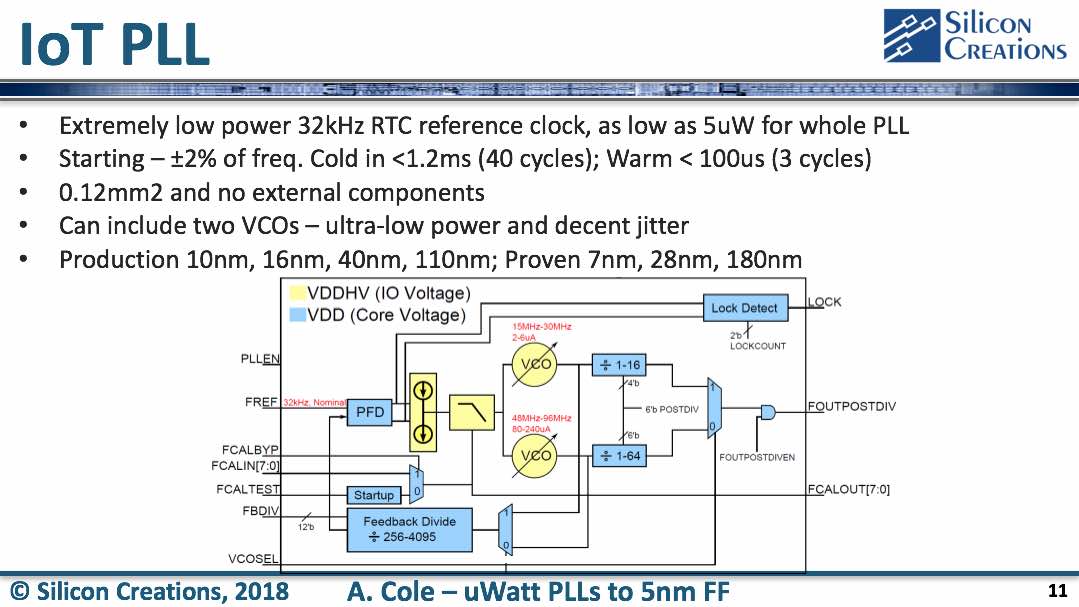

Essential Analog IP for 7nm and 5nm at TSMC OIP

When TSMC’s annual Open Innovation Platform Exposition takes place, you know it will be time to hear about designs starting on the most advanced nodes. This year we were hearing about 7nm and 5nm. These newer nodes present even more challenges than previous nodes due to many factors. Regardless of what kind of design you are undertaking… Read More

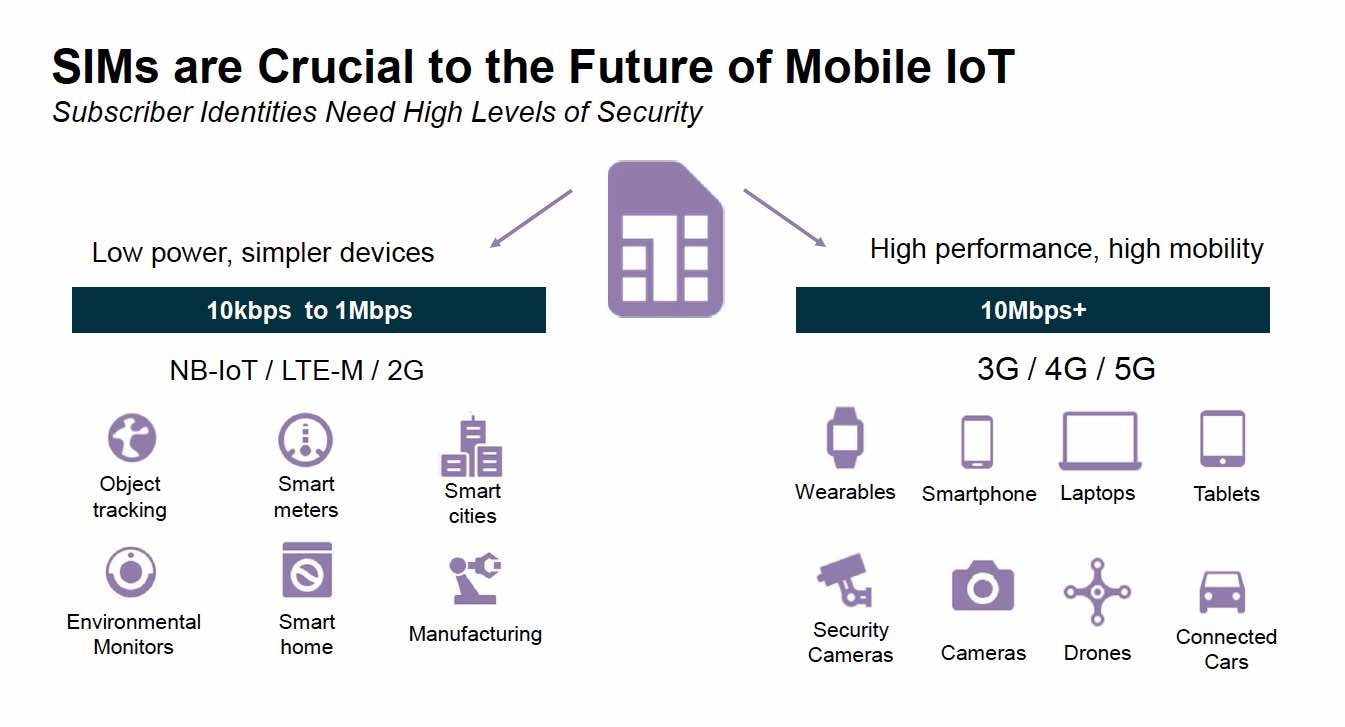

Synopsys Seeds Significant SIM Segue

It turns out that consumers are not alone in their love-hate relationship with SIM cards. SIM cards save us from increasingly widespread cellphone cloning. However, if your experience is anything like mine, it seemed that with every new phone, a new SIM card format was needed. Furthermore, people travelling overseas who wanted… Read More

An FPGA Industry Veteran’s View of Future

There are tectonic changes happening in the world of FPGAs. A lot has changed since their introduction in the 80’s. Back then they were mostly used to implement state machines or glue logic. Subsequently they grew more complex with the addition of high speed IOs, eRAM, DSPs, other processors and other IP. More recently though FPGAs… Read More

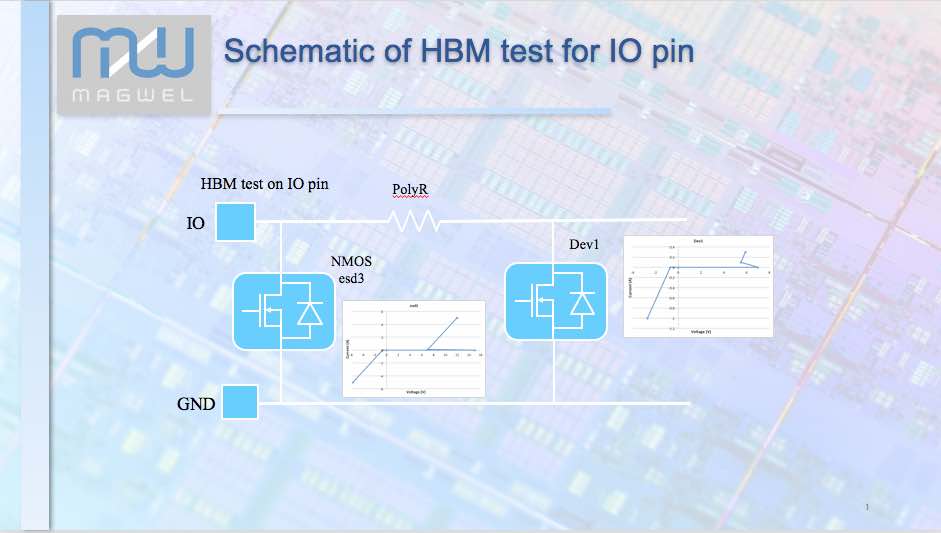

Verifying ESD Fixes Faster with Incremental Analysis

The author of this article, Dündar Dumlugöl, is CEO of Magwel. He has 25 years of experience in EDA managing the development of leading products used for circuit simulation and high-level system design.

Every designer knows how tedious it can be to shuttle back and forth between their layout tool and analysis tools. Every time an… Read More

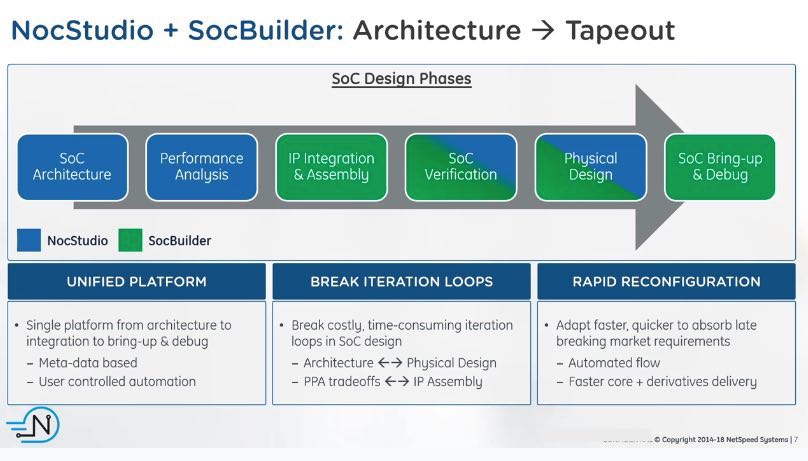

Webinar: NetSpeed is about to change the way SOCs are designed

A large part of the effort in designing SOCs has shifted to the integration of their constituent IP blocks. Many IP blocks used in SOCs come as ready to use components and the real work has become making them work together. Network on Chip (NoC) has been a huge help in this task, handling the interconnections between blocks and planning… Read More

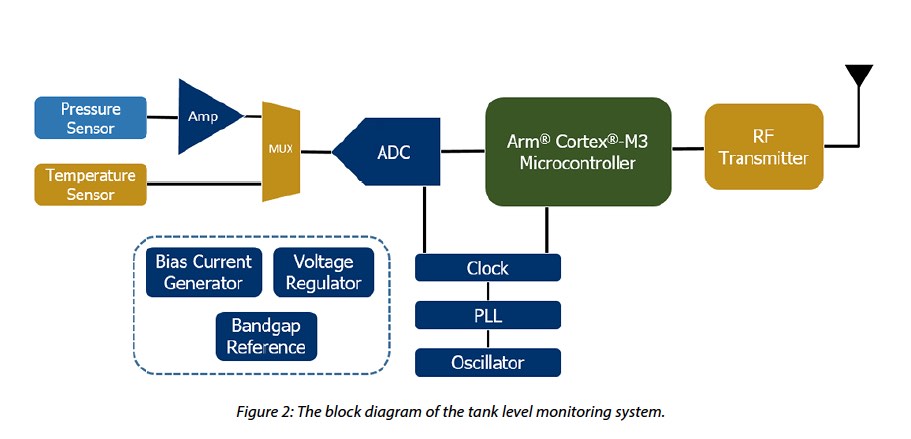

Living on the (IoT) Edge

The phrase “where the rubber meets the road” is especially apt when it comes to discussions about the Internet of Things. The obvious interpretation is that dissimilar things are being put together in a mutually dependent fashion. When I hear the phrase I always think of the things that can go wrong, such a tire sliding instead of … Read More

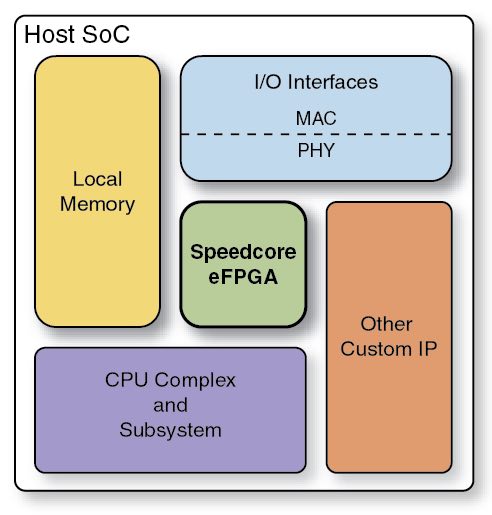

Timing Closure Techniques for SOCs with Embedded FPGA Fabric

Once the benefits of using an embedded FPGA fabric are understood, the next question is about how timing closure is handled between the ASIC and the eFPGA blocks. First let’s look briefly at the advantages. By moving the eFPGA on to the SOC die, tons of I/O logic and the need for any package and board interconnect will vanish. Package… Read More

Netspeed and NSITEXE talk about automotive design trends at 55DAC

DAC is where both sides of the design equation come together for discussion and learning. This is what makes attending DAC discussion panels so interesting; you are going to hear from providers of tools, methodologies and IP as well as those who need to use them to deliver working solutions. There are few places where the interplay… Read More

Breker Hosts an Energetic Panel on Spec-Driven Verification