At the recent TSMC OIP symposium, a collaborative presentation by Synopsys and Xilinx highlighted the importance of incorporating the local FinFET device self-heating temperature increase on the acceleration of device reliability mechanisms.… Read More

Author: Tom Dillinger

Extendible Processor Architectures for IoT Applications

The Internet of Things has become a ubiquitous term, to refer to a broad (and somewhat ill-defined) set of electronic products and potential applications – e.g., wearables, household appliances and controllers, medical applications, retail applications (signage, RFID), industrial automation, machine-to-machine communication,… Read More

Wafer-Level Chip-Scale Packaging Technology Challenges and Solutions

At the recent TSMC OIP symposium, Bill Acito from Cadence and Chin-her Chien from TSMC provided an insightful presentation on their recent collaboration, to support TSMC’s Integrated FanOut (InFO) packaging solution. The chip and package implementation environments remain quite separate. The issues uncovered in bridging… Read More

Optimizing Quality-of-Service in a Network-on-Chip Architecture

The Linley Group is well-known for their esteemed Microprocessor Report publication, now in its 28th year. Accompanying their repertoire of industry reports, TLG also sponsors regular conferences, highlighting the latest developments in processor architecture and implementation.

One of the highlights of the conference… Read More

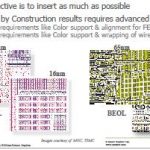

Meeting DFM Challenges with Hierarchical Fill Data Insertion

To describe the latest methodology for the addition of Design for Manufacturability fill shapes to design layout data, it’s appropriate to borrow a song title from Bob Dylan – The Times They Are A Changin’. The new technical requirements are best summarized as: “The goal is now to add as much fill as possible, which (ideally) looks… Read More

A FinFET BSIM-CMG model update from UC-Berkeley

Every designer relies upon an underlying “compact” device model for circuit simulations – these models are the lifeblood of the IC industry. Designers may not be aware that there is an organization that qualifies models – the Compact Model Coalition – which operates under the umbrella of the Si2 Consortium: http://www.si2.org/cmc_index.php… Read More

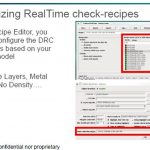

Top 10 Reasons to invest in Interactive Design Rule Checking tools

One of the most energetic presentations at the recent TSMC OIP 2015 symposium was given by Tom Williams from Qualcomm, who shared his insights (and enthusiasm!) for Mentor’s Calibre RealTime interactive Design Rule Checking (iDRC) product.

Paraphrasing Tom’s presentation (and with a tip of the hat to David Letterman), here … Read More

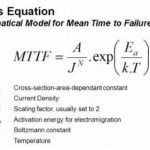

Electromigration Analysis and FinFET Self-Heating

FinFET processes provide power, performance, and area benefits over planar technologies. Yet, a vexing problem aggravated by FinFET’s is the greater local device current density, which translates to an increased concern for signal and power rail metal electromigration reliability failures. There is a critical secondary… Read More

Four Takeaways from the TSMC OIP 2015

Paul M. did an excellent job summarizing the technical information that TSMC presented at the recent Open Innovation Platform symposium. I’d like to also share an impression on four areas that struck me as key to TSMC’s strategy.… Read More

What’s the Difference between Emulation and Prototyping?

Increasing system complexity requires constant focus on the optimal verification methodology. Verification environments incorporate a mix of: transaction-based stimulus and response monitors, (pseudo-)random testcase generation, and ultimately, system firmware and software. RTL statement and assertion coverage… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center