Last month India Electronics & Semiconductor Association (IESA) held its Vision Summit at Bangalore in which luminaries from across the semiconductor and electronics industry presented their views about the future of this industry and India’s progress. Dr. Walden C. Rhines, Chairman and CEO of Mentor Graphicspresented… Read More

Author: Pawan Fangaria

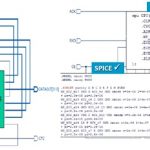

Mixed-Signal SoC Debugging & IP Integration Made Easy

A semiconductor SoC design can have multiple components at different levels of abstractions from different sources and in different languages. While designing an SoC, IPs at different levels have to be integrated without losing the overall design goals. Of course, quality of an IP inside and outside of an SoC must be tested thoroughly.… Read More

TI’s Way of Strategies – Formation & Execution

For a company to stand still and continually prosper even after facing several downturns in its career of 80+ years, and still move swiftly with strong commitment and confidence, its strategy has to be right and rock solid possessing sustainable competitive advantage, and of course it has to be an early mover in everything it does… Read More

Carbon Design Systems – Secret of Success

Last week, after learning from the press releaseof Carbonabout its rocking sustained growth with record-breaking revenue and a thumping 46% increase in bookings, I was interested to know some more details about what drives Carbon to such an amazing performance in an EDA market that is generally prone to growth of a few percentage… Read More

Is Smartphone Market Maturing?

Yes and No, in my view. Yes to a certain extent, considering that most of the people in developed world have more than one (may be with dual sim card) phone; and No, considering the vast untapped market in the third world countries of Asia and Africa. In India, although much of the population (who can afford a phone) has phone, but not … Read More

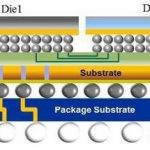

Smart Strategies for Efficient Testing of 3D-ICs

3D-IC has a stack of dies connected and packaged together, and therefore needs new testing strategies other than testing a single die. It’s given that a single defective die can render the whole of 3D-IC unusable, so each die in the stack must be completely and perfectly tested before its entry into that stack. Looking at it from a … Read More

TI – The Initial Innovator of Semiconductor ICs

[TI’s China Foundry acquired from SMIC]

During my engineering graduation, electronic design courses and mini-projects, the ICs I used to come across were SN 7400 series from Texas Instrumentsthat covered a large range of devices from basic gates and flip-flops to counters, registers, memories, ALUs, system controllers, and… Read More

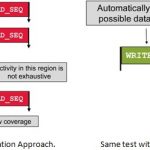

SoC Verification Closure Pushes New Paradigms

In the current decade of SoCs, semiconductor design size and complexity has grown by unprecedented scale in terms of gate density, number of IPs, memory blocks, analog and digital content and so on; and yet expected to increase further by many folds. Given that level of design, it’s imperative that SoC verification challenge has… Read More

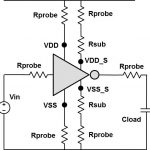

Dual Advantage of Intelligent Power Integrity Analysis

Often it is considered safer to be pessimistic in estimating IR-drop to maintain power integrity of semiconductor designs; however that leads to the use of extra buffering and routing resources which may not be necessary. In modern high speed, high density SoCs having multiple blocks, memories, analog IPs with different functionalities… Read More

Grid Vision 2050 – Unified & Open Across The Globe

Whenever there is good momentum in a particular technology, IEEEtakes major initiative to standardize the procedures, formats, methods, measurements etc. involved in the technology to proliferate it for the advantage of wider community. And that becomes successful by active participation and collaboration of both producers… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era