An SoC can have a collection of multiple blocks and IPs from different sources integrated together along with several other analog and digital components within a native environment. The IPs can be at different levels of abstractions; their RTL descriptions can be in different languages such as Verilog, VHDL, or SystemVerilog.… Read More

Author: Pawan Fangaria

Multi-Level Debugging Made Easy for SoC Development

HW/SW Interfaces for Portable Stimulus

With growing size and complexity of SoC, the semiconductor community is realizing the growing pain of verification. The cost of SoC verification grows exponentially with design size. Moreover, there is no single methodology for verifying a SoC; multiple engines are used in different contexts through different verification… Read More

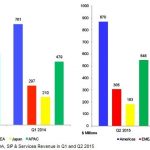

Semiconductor, Oil, and GDP – Correlated? What’s Expected?

In last 3 decades of semiconductor market, the largest growth in IC sales was at 33% in 2010. At that time global recession had started due to financial crisis and in 2009 oil prices fell more than 30%. It appeared that oil prices were negatively correlated with semiconductor market growth. Today again there is another sharp decline… Read More

Synopsys’ New Circuit Simulation Environment Improves Productivity — for Free

When technology advances, complexities increase and data size becomes unmanageable. Fresh thinking and a new environment for automation are needed to provide the required increase in productivity. Specifically in case of circuit simulation of advanced-node analog designs, where precision is paramount and a large number… Read More

Cadence Adds New Dimension to SoC Test Solution

It requires lateral thinking in bringing new innovation into conventional solutions to age-old hard problems. While the core logic design has evolved adding multiple functionalities onto a chip, now called SoC, the structural composition of DFT (Design for Testability) has remained more or less same based on XOR-based compression… Read More

5nm Chips? Yes, but When?

For any invention, technical proof of concept or prototyping happens years ahead of the invention being infused into actual products. When we talk about 5nm chip manufacturing, a test chip was already prototyped in last October, thanks to Cadence and Imec. Details about this chip can be found in a blog at Semiwiki (link is given … Read More

Decisive Floorplanning for Faster Design Closure

Semiconductor design automation at system level is gaining its due importance today. It needs an effective, efficient, and seamless flow from system up to silicon. There is lot of effort going on for automating SoC design exploration at system level but that eventually stops at RTL; another level of flow automation takes over … Read More

Pure-play Foundries to Prevail in Future

In a consolidating semiconductor business environment and innovation in semiconductor fabrication already scaling new heights with existing strong players, where do you think the wafer capacity should concentrate? It’s pure-play foundries or pure-play-like foundries, and those who supply high-volume common components… Read More

Urban Mobility – Innovative Solutions to Tough Challenges

Challenges of urban mobility are not only traffic congestion and accidents, but also pollution level, energy efficiency, cleaner, safer, and reliable environment. Cities in Asian region, specifically India and China are struggling to control extra-high level of pollution on this date. In Delhi, the first brute force attempt… Read More

IP Development in Japan

As semiconductor IP is growing bigger in size and more complex in providing complete solution for a particular functionality in an SoC, regions from across the world are joining to provide various types of services in the overall value-chain of IP development, verification, and its integration into SoCs. … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center