Suk Lee drew the short straw at the TSMC Symposium yesterday, with the 5pm slot. Not only late in the day but between all the attendees and free beer. The morning sessions had been standing room only, with several hundred standees (as they call them on muni around here, but isn’t a standee really someone being stood on?). But … Read More

Author: Paul McLellan

Mentor U2U, Not Your Father’s User Conference

I talked to Michael Buehler-Garcia about the changes Mentor is making to U2U, their user conference. It is in San Jose on April 25th at the DoubleTree.

Firstly, there are 3 great keynotes, two of whom I’ve seen speak before and can unreservedly recommend. Unfortunately I’m traveling that week and won’t be able… Read More

Cadence Sues Berkeley Design Automation

Cadence has brought a suit against Berkeley Design Automation for, as far as I can see, integrating their AFS circuit simulator with the Virtuoso Analog Design Environment (ADE) without using the (licensed) Oasis product. Since BDA is (actually was) a member of the Cadence Connections program, they have to abide by the contract… Read More

GlobalFoundries in Singapore

I hosted a webinar today for GlobalFoundries. Yes, I know that today was TSMC’s Technology Symposium, we weren’t that smart when we picked the date. It was basically a “fireside chat” with me as the moderator asking the questions and Paul Colestock and Aabid Husain as my guests. We actually did it at Cadence… Read More

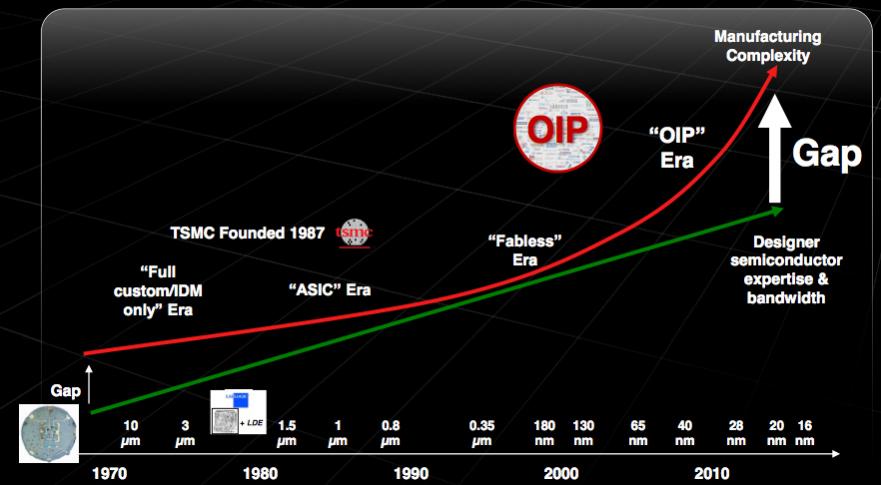

How Long Does it Take to Go From a Muddy Field to Full 28nm Capacity?

TSMC has a lot of capacity. Not just that, it has a lot more under construction. It currently has 3 300mm Gigafabs, fabs 12,14 and 15 (there doesn’t seem to be a 13). This morning, Dr Wang, who is TSMC’s VP of 300mm operations told us about the expansion plans. Currently fab 15 phase 3 and 4, and fab 12 phase 3 are to be ramped… Read More

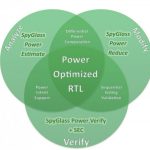

RTL Power Optimization

More so than most aspects of design, power reduction suffers from a paradox that early in the design cycle when the gains are the largest, the accuracy of power estimation is the lowest, and then late in the design cycle, when everything is known pretty much exactly it is too late to make anything other than trivial optimizations. … Read More

GSA Silicon Summit: More than Moore

The theme of this year’s GSA Silicon Summit is More than Moore. This has become a sort of catchall phrase for technologies other than simply moving to the next process node. The summit is on April 18th at the computer history museum (1401 Shoreline Blvd). Registration takes place at 9am and the actual sessions start at 9.45am.… Read More

Kathryn Kranen Wins UBM Lifetime Achievement Award 2013

UBM’s EETimes and EDN today announced Kathryn Kranen as the lifetime achievement award winner for this years ACE awards program. Kathryn, of course, is the CEO of Jasper (and is also currently the chairman of EDAC). Past winners exemplify the prestige and significance of the award. Since 2005 the award was given to Gordon… Read More

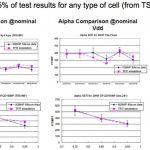

Cell Level Reliability

I blogged last month about single event effects (SEE) where a semiconductor chip behaves incorrectly due to being hit by an ion or a neutron. Since we live on a radioactive planet and are bombarded by cosmic rays from space, this is a real problem, and it is getting worse at each process node. But just how big of a problem is it?

TFIT is … Read More

Phil Kaufman Award Recipient 2013: Chenming Hu

This year’s recipient of the Kaufman Award is Dr Chenming Hu. I can’t think of a more deserving recipient. He is the father of the FinFET transistor which is clearly the most revolutionary thing to come along in semiconductor for a long time. Of course he wasn’t working alone but he was the leader of the team at UC… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center