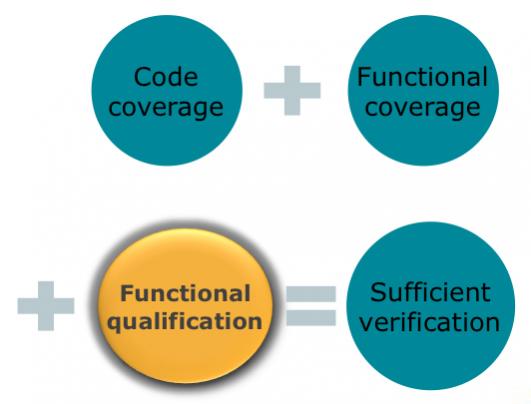

The traditional way for analyzing the effectiveness of testing in the software world and in the RTL world is code coverage. Make sure that every line of code is executed. This is a pretty crude measure since even 100% code coverage doesn’t mean that all the condition has really been tested but it is certainly necessary–after… Read More

Author: Paul McLellan

SOC Realization: How Chips Are Really Designed

If you just casually peruse most marketing presentations by EDA companies, you’d come to the conclusion most SoCs are designed from scratch, wrestlilng the monster to the ground with bare hands. But the reality is that most SoCs consist of perhaps 90% IP blocks (many of them memories). That still leaves the remaining 10% … Read More

40nm to 28nm Migration Success Story

The problem:To move dual-port SRAM library and macros from a 40nm process to a 28nm process. In addition to all the changes between two different foundry processes, the 28nm rules are disruptive and incompatible with the previous rules. The memory corecells (foundry-specific) would also need to be completely replaced.

Current… Read More

Intel’s 22nm Process. Atom, ARM, Apple

Intel had a big press event yesterday at which they announced details of their 22nm process. In a change from their current processes, it goes with a vertical gate. In fact 3 gates which gives them much better control of leakage through transistors that are switched off, along with more transmission through the on transistors. They… Read More

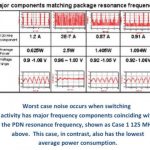

Chip Power Models

As the complexity of the chip-package-system (CPS) interactions has increased, the tradeoffs in doing a power and noise analysis has had to gradually increase. As is so often the case in semiconductor designs, issues first arise as second-order effects that can largely be ignored but each process node makes the problem worse … Read More

Apache at DAC

DAC is less than a month away, June 6-8th for the tradeshow, longer depending on what other events you might also be attending. Apache is in booth 2448 (marked in red on the DAC floorplan map.

Many of the presentations at the Apache booth will be customers (such as ARM, Xilinx, ST Ericsson, GlobalFoundries and TSMC) discussing various… Read More

Ivo Bolsens of Xilinx and Crossover Designs

I was at Mentor’s u2u (user group) meeting and one of the keynotes was by Ivo Bolsens of Xilinx. The other was by Wally Rhines and is summarized here.

Ivo started off talking analogizing SoCs as the sports-cars of the industry (fast but expensive), and FPGAs as the station wagons (not cool). In fact he even said that when Xilinx… Read More

Wally’s u2u keynote

I was at Wally’s u2u (Mentor user group) keynote yesterday. The other keynote was by Ivo Bolsens of Xilinx and is here. He started off by looking at how the semiconductor industry has recovered and silicon area shipments are now back on trend after a pronounced drop in 2009 and revenue has followed. Finally the semiconductor… Read More

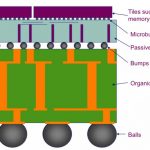

The World’s Smallest Printed Circuit Boards: interposers

Have you ever had the experience where you look up some unusual word in the dictionary since you don’t remember seeing it before. And then, in the next few weeks you keep coming across it. Twice in the last week I have been in presentations about the economics of putting die onto silicon interposers and the possibility of a new… Read More

Semiconductor RTL Power Analysis: the sweet spot

Power has become the strongest driver of semiconductor design today, more important than area, more important than timing. Whether the device is handheld, like a wireless phone, or tethered, like a router, complex power and energy requirements must be met. Shrinking geometries continue to impose new challenges as power management… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center